# 1994 (REV. 2)

# CRYSTAL SEMICONDUCTOR COMMUNICATION DATABOOK

# MODEL INDEX

| CS2180A/B        | 3-5  |

|------------------|------|

| CS3310           | 8-5  |

| CS4215           |      |

| CS4216           | 10-5 |

| CS4225           |      |

| CS4231           |      |

| CS4231A          |      |

| CRD4231          |      |

| CS4248           |      |

| CS4303           |      |

| CS4328           |      |

| CS4330/1/3       |      |

| CS4920           |      |

| CS5012A/4/6      |      |

| CS5030/1         |      |

| CS5032           |      |

| CS5101A/2A       |      |

| CS5317           |      |

| CS5321           |      |

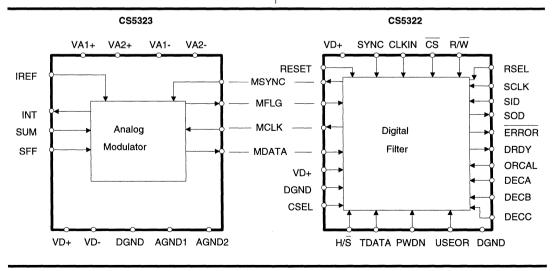

| CS5322/23        |      |

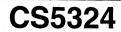

| CS5324           |      |

| CS5330/1         |      |

| CS5336/8/9       |      |

| CS5349<br>CS5389 |      |

| CS5389           |      |

| CS5390           |      |

| CS5412           |      |

| CS5490           |      |

| CS5501/3         |      |

| CS5504           |      |

| CS5505/6/7/8     |      |

| CS5509           |      |

| CS5516/20        |      |

| CS61304A         |      |

| CS61305A         |      |

| CS6152           |      |

| CDB6152          |      |

|                  |      |

| CS61534       | 3-127   |

|---------------|---------|

| CS61535/5A    | 3-147   |

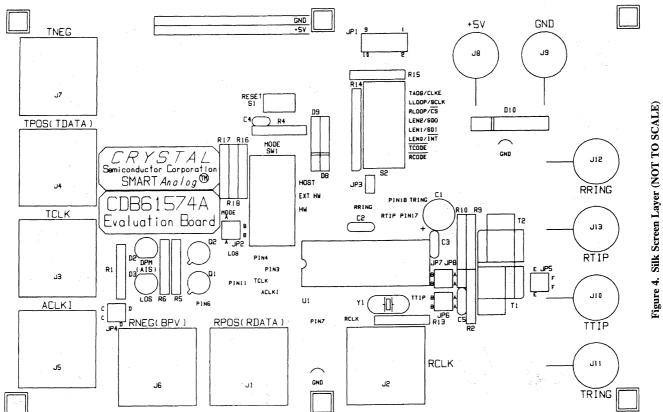

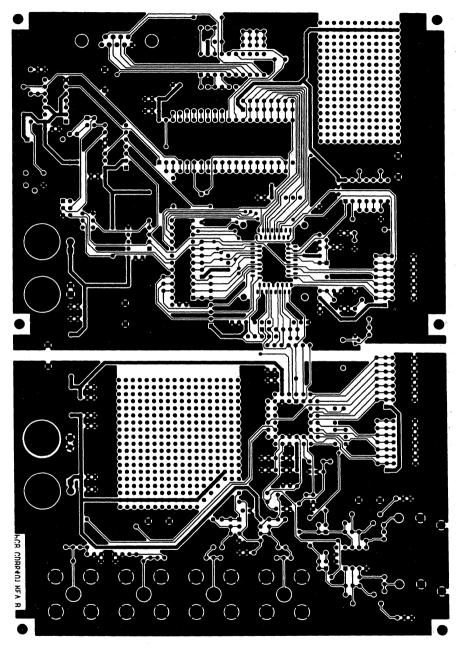

| CDB61534/5/5A | 3-299   |

| CS61544       | 3-181   |

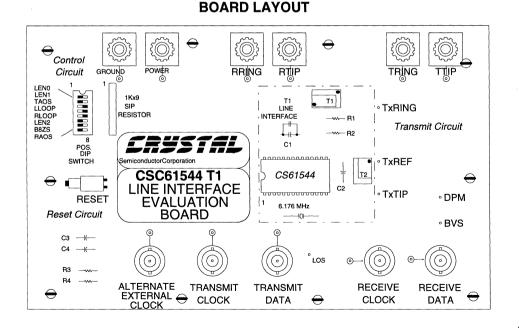

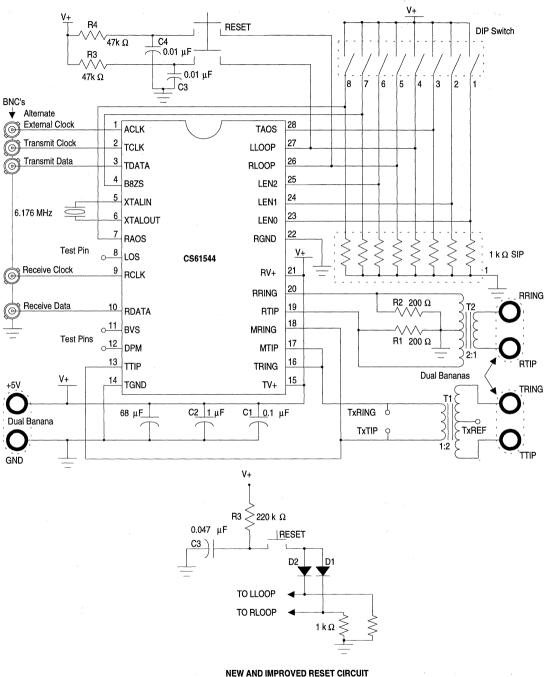

| CDB61544      | 3-197   |

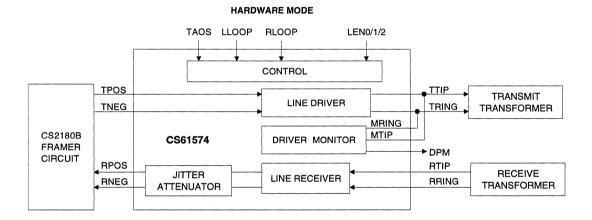

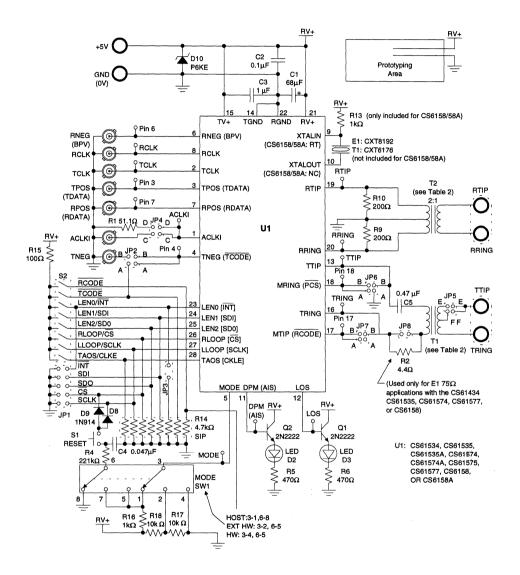

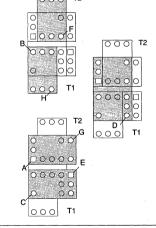

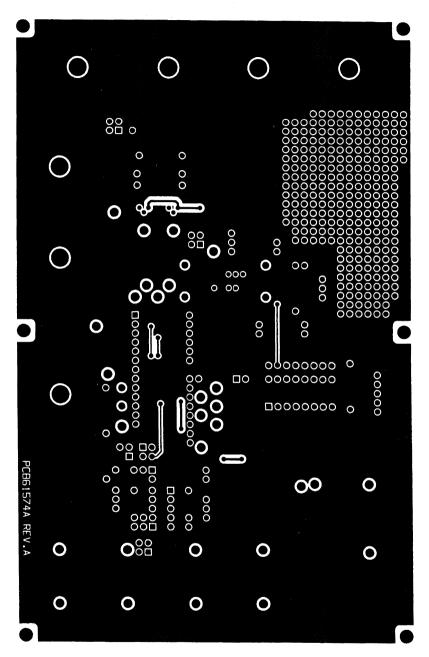

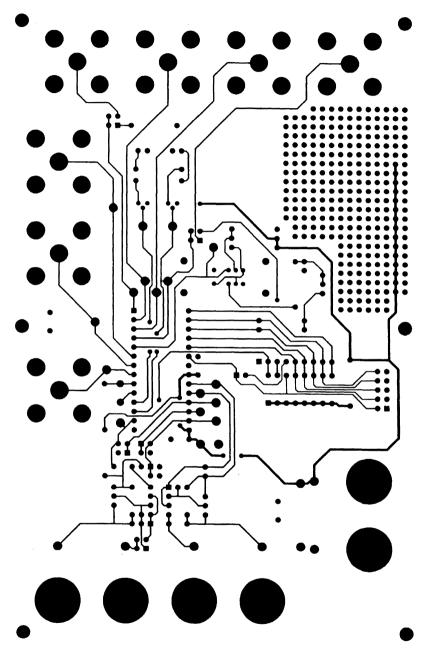

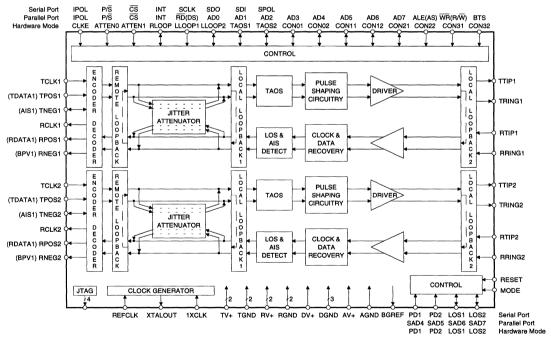

| CS61574       | 3-199   |

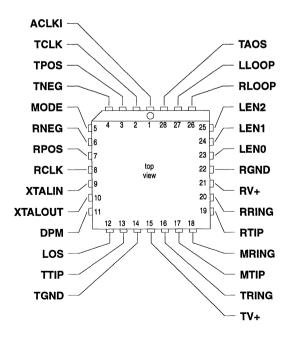

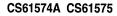

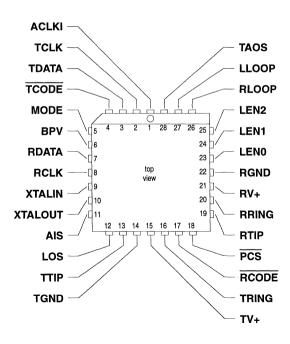

| CS61574A/5    | 3-221   |

| CDB61574/4A/5 | 3-299   |

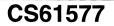

| CS61577       | 3-251   |

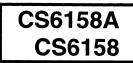

| CS6158/8A     | 3-281   |

| CDB6158/8A    | 3-299   |

| CS61584       |         |

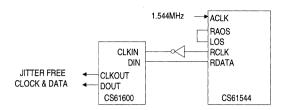

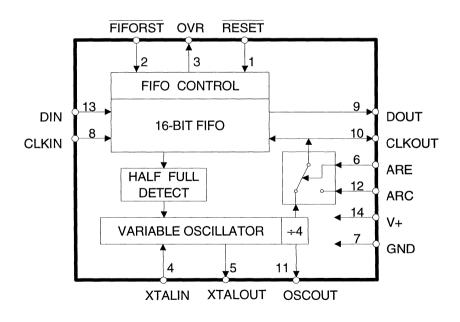

| CS61600       | 4-3     |

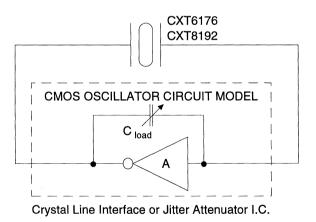

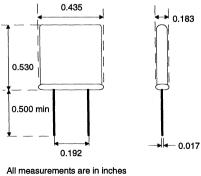

| CXT6176/8192  | 3-359   |

| CS6400        | 6-3     |

| CS6401        | 6-37    |

| CDB6401       | 6-60    |

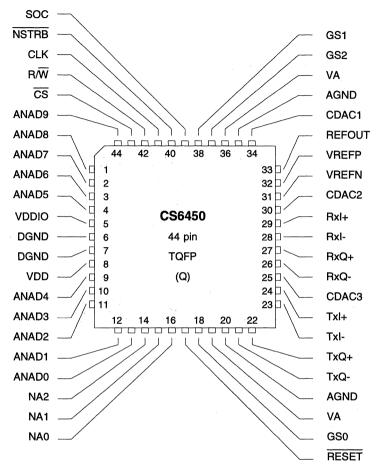

| CS6450        | 6-89    |

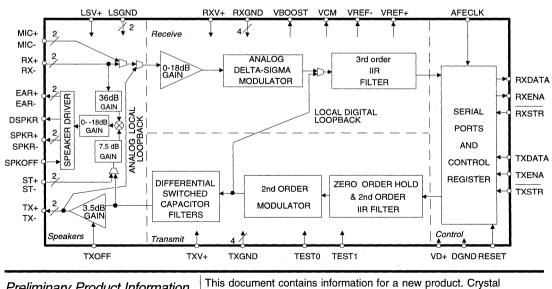

| CS6453        |         |

| CS7870/5      |         |

| CS80600       | 4-15    |

| CS8130        | 7-3     |

| CS83C92A/C    |         |

| CS8401A/2A    | 8-15    |

| CS8411/2      |         |

| CS8425        | 8-17    |

| CS8870        |         |

| CS8900        | 2-17    |

| CS8905        |         |

| CS9203        | . 10-16 |

| CRD9203       |         |

| CRD9203R      | . 10-18 |

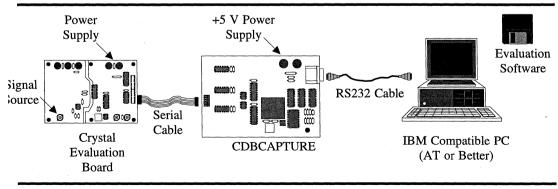

| CDBCAPTURE    |         |

| CWDRGNTT      |         |

| CWECAXB       | 6-83    |

| CWMNLG        | . 10-13 |

| DIAGNOSTICS   | 10-11   |

| DRIVERS       | . 10-10 |

# **Crystal Semiconductor Corporation**

# Communication Products Data Book

# October 1994

This publication neither states nor implies any warranty of any kind, including, but not limited to, implied warrants of merchantability or fitness for a particular application. Crystal assumes no responsibility for the use of any circuitry other than the circuitry in a Crystal product. No circuit patent licenses are implied.

The information in this publication is believed to be accurate in all respects at the time of publication but is subject to change without notice. Crystal assumes no responsibility for errors and omissions, and disclaims responsibility for any consequences resulting from the use of information included herein. Additionally, Crystal assumes no responsibility for the functioning of undescribed features or parameters.

© Copyright 1994 Crystal Semiconductor Corporation

#### LIFE SUPPORT AND NUCLEAR POLICY

CRYSTAL SEMICONDUCTOR PRODUCTS ARE NOT AUTHORIZED FOR AND SHOULD NOT BE USED WITHIN LIFE SUP-PORT SYSTEMS OR NUCLEAR FACILITY APPLICATIONS WITHOUT THE SPECIFIC WRITTEN CONSENT OF CRYSTAL SEMICONDUCTOR.

Life Support Systems are equipment intended to support or sustain life and whose failure to perform when properly used in accordance with instructions provided can be reasonably expected to result in personal injury or death. Users contemplating applications of Crystal Semiconductor products in Life Support Systems are requested to contact Crystal Semiconductor factory headquarters to establish suitable terms and conditions for these applications. Crystal Semiconductor's warranty is limited to replacement of defective components and does not cover injury to persons or property or other consequential damages.

Examples of devices considered to be life support devices are neonatal oxygen analyzers, nerve stimulators (whether used for anesthesia, pain relief, or other purposes), autotransfusion devices, blood pumps, defibrillators, arrhythmia detectors and alarms, pacemakers, hemodialysis systems, peritoneal dialysis systems, neonatal ventilator incubators, ventilators for both adults and infants, anesthesia ventilators, and infusion pumps, as well as other devices designated as "critical" by the FDA. The above are examples only and are not intended to be conclusive or exclusive of any other life support device.

Examples of nuclear facility applications are applications in (a) a nuclear reactor, or (b) any device designed or used in connection with the handling, processing, packaging, preparation, utilization, fabricating, alloying, storing, or disposal of fissionable material or waste products thereof.

1

# TRADEMARKS

Crystal Semiconductor Corporation has made every effort to supply trademark information about company names, products, and services mentioned in this book. Trademarks indicated below are derived from various sources.

CRYSTAL is a registered trademark of Crystal Semiconductor Corporation.

SMART Analog, Crystal Clear, and CrystalWare are trademarks of Crystal Semiconductor Corporation.

Trademarks in this book belong to their respective companies.

## PATENTS

Products in this book may be covered by one or more of the following patents. Additional patents are pending.

#### <u>U.S.A.:</u>

4,709,225; 4,746,899; 4,748,418; 4,804,863; 4,805,198; 4,849,662; 4,851,841; 4,918,454; 4,939,516; 4,941,156; 4,943,807; 4,988,954; 5,012,244; 5,039,989; 5,055,846; 5,061,925; 5,068,660; 5,079,550; 5,087,914; 5,088,107; 5,111,451; 5,117,200; 5,121,080; 5,140,279; 5,150,386; 5,157,395; 5,172,115; 5,187,390; 5,196,850; 5,198,782; 5,208,597; 5,212,659; 5,220,483; 5,239,210; 5,245,344; 5,247,210; 5,248,970; 5,257,026; 5,258,758; 5,268,651; 5,274,375.

#### Germany:

3,642,070; 3,733,682; 3,736,735; 3,737,279; 3,933,552; 4,002,871; 4,127,096; 4,202,180.

#### Great Britain:

2,184,621; 2,195,848; 2,198,305; 2,198,306; 2,223,879; 2,232,547.

#### France:

2,591,753; 2,604,839; 2,606,564; 2,606,565; 2,673,779.

#### Japan:

1,684,670; 1,736,807; 1,747,991.

| CRYSTAL            | COMMUNICATIONS DATA BOOK CONTENTS                                                                                  |    |

|--------------------|--------------------------------------------------------------------------------------------------------------------|----|

|                    | GENERAL INFORMATION                                                                                                | 1  |

| LAN:               | ETHERNET PRODUCTS<br>10 Base-T ISA Controller<br>Ethernet/Cheapernet Transceiver                                   | 2  |

| TELECOM:           | T1 / E1 PRODUCTS<br>T1 Framers<br>T1/E1 Line Interface ICs<br>Quartz Crystals                                      | 3  |

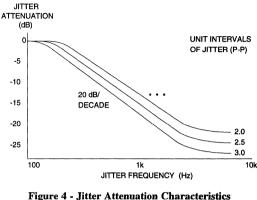

|                    | JITTER ATTENUATORS                                                                                                 | 4  |

|                    | DTMF RECEIVER                                                                                                      | 5  |

| SIGNAL PROCESSING: | VOICEBAND & BASEBAND PRODUCTS<br>Echo Cancellers<br>TDMA Baseband Cellular CODEC<br>Modem / Audio Analog Front-end | 6  |

| DATACOM:           | INFRARED TRANSCEIVER                                                                                               | 7  |

| OTHER PRODUCTS:    | CONSUMER AUDIO PRODUCTS                                                                                            | 8  |

|                    | DATA ACQUISITION PRODUCTS                                                                                          | 9  |

|                    | MULTIMEDIA AUDIO PRODUCTS                                                                                          | 10 |

| MISCELLANEOUS:     | APPLICATION NOTES                                                                                                  | 11 |

|                    | APPENDICES<br>Reliability Calculation Methods<br>Package Mechanical Drawings                                       | 12 |

|                    | SALES OFFICES                                                                                                      | 13 |

| 1. | GENERAL INFORMATION                                 |                |

|----|-----------------------------------------------------|----------------|

|    | - Contents                                          |                |

|    | - Product Overview                                  |                |

|    | - Company Information and Part Numbering Convention |                |

|    | - Quality and Reliability Information               | 1              |

|    |                                                     | -              |

| 2. | ETHERNET/CHEAPERNET                                 |                |

|    | - Introduction and Contents                         |                |

|    | - CS83C92A/C Coaxial Transceiver Interface          |                |

|    | - CS8900 Highly-Integrated ISA Ethernet Controller  | 7              |

|    |                                                     | '              |

| 3. | T1/E1/ISDN PRIMARY RATE                             |                |

| 5. | - Introduction and Contents                         |                |

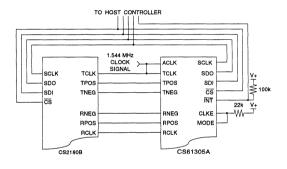

|    | - CS2180A/B T1 Transceivers                         |                |

|    | - $CSE1204A$ T1/E1 Line Interface                   | <b>`</b>       |

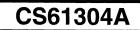

|    | - CS61304A T1/E1 Line Interface                     | -              |

|    | - CS61305A T1/E1 Line Interface                     | -              |

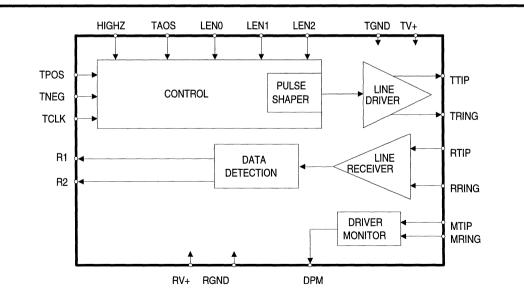

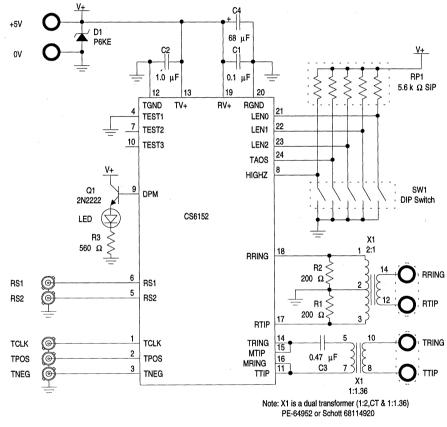

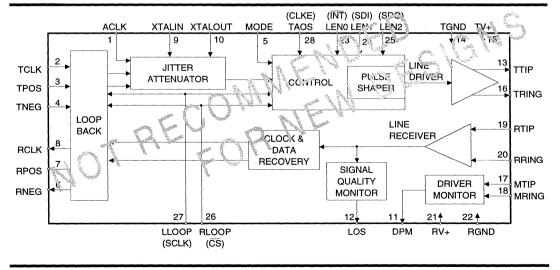

|    | - CS6152 T1 Analog Interface                        |                |

|    | - CDB6152 Evaluation Board                          |                |

|    | - CS61534 T1/E1 Line Interface                      |                |

|    | - CS61535/5A T1/E1 Line Interface                   |                |

|    | - CS61544 T1 Line Interface                         | 31             |

|    | - CDB61544 Evaluation Board                         | 97             |

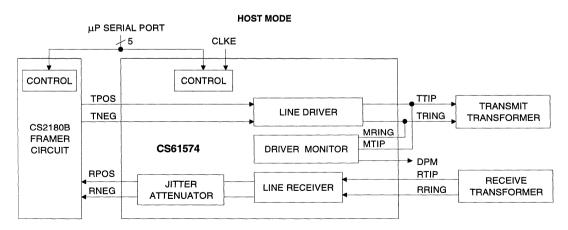

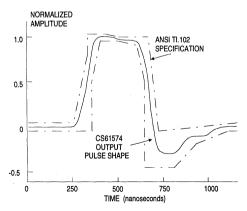

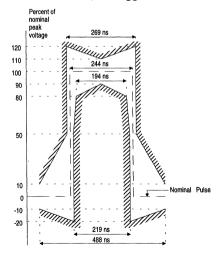

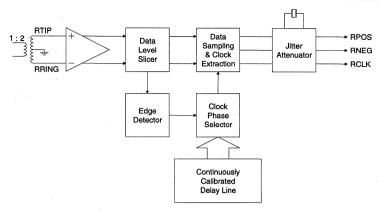

|    | - CS61574 T1/E1 Line Interface                      | <del>9</del> 9 |

|    | - CS61574A/75 T1/E1 Line Interface                  | 21             |

|    | - CS61577 T1/E1 Line Interface                      | 51             |

|    | - CS6158/58A T1/E1 Line Interface                   | 81             |

|    | - CDB61534/35/35A/74/74A/75/58/58A Evaluation Board | 99             |

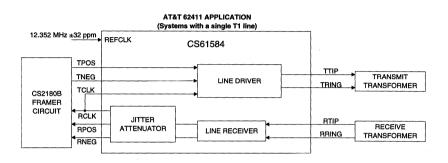

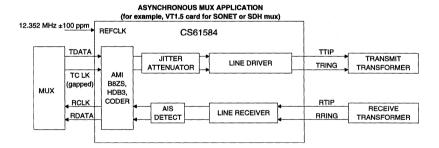

|    | - CS61584 Dual, Low Power T1/E1 Line Interface      | 09             |

|    | - CXT6176/8192 Crystals                             | 59             |

|    |                                                     |                |

| 4. | JITTER ATTENUATORS                                  |                |

|    | - Introduction and Contents                         |                |

|    | - CS61600 PCM Jitter Attenuator                     |                |

|    | - CS80600 High Speed Jitter Attenuator              |                |

|    |                                                     | 5              |

| 5. | DUAL TONE MULTI FREQUENCY (DTMF) RECEIVERS          |                |

| 5. | - Introduction and Contents                         |                |

|    | - CS8870 DTMF Receiver                              |                |

|    |                                                     |                |

| 6. | VOICEBAND & BASEBAND PRODUCTS                       |                |

| 0. | - Introduction and Contents                         |                |

|    |                                                     |                |

|    |                                                     |                |

|    | - CS6401 Programmable Echo Canceller                |                |

|    | - CDB6401 Evaluation Board                          | -              |

|    | - CWECAXB Executable Code for the CS6401            | -              |

|    | - CS6450 TDMA/AMPS I&Q Baseband CODEC               | -              |

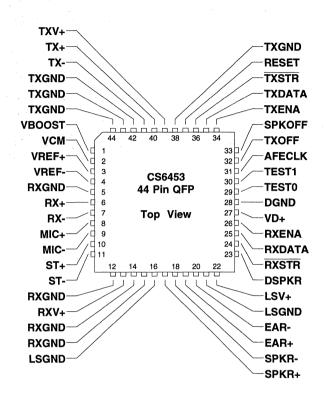

|    | - CS6453 Modem and Audio Analog Front-End           | 09             |

# CRYSTAL

| 7. | PERSONAL COMMUNICATIONS PRODUCT                                                                          |   |   |   |   |   |   |   |      |

|----|----------------------------------------------------------------------------------------------------------|---|---|---|---|---|---|---|------|

|    | - Introduction and Contents                                                                              |   |   |   |   |   |   |   | 7-2  |

|    | - CS8130 Multi-Standard Infrared Transceiver                                                             | • | • | • | • | • | • | • | 7-3  |

| 8. | CONSUMER & PROFESSIONAL AUDIO PRODUCTS                                                                   |   |   |   |   |   |   |   |      |

|    | - Introduction and Contents                                                                              |   |   |   |   |   |   |   | 8-2  |

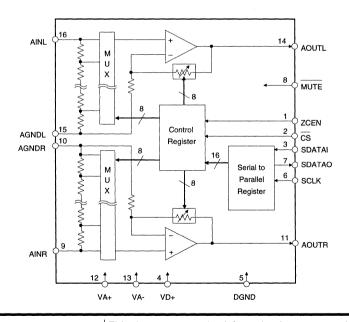

|    | - CS3310 Stereo Digital Volume Control                                                                   |   |   |   |   |   |   |   | 8-5  |

|    | - CS4225 Digital Audio Conversion System                                                                 |   |   |   |   |   |   |   | 8-6  |

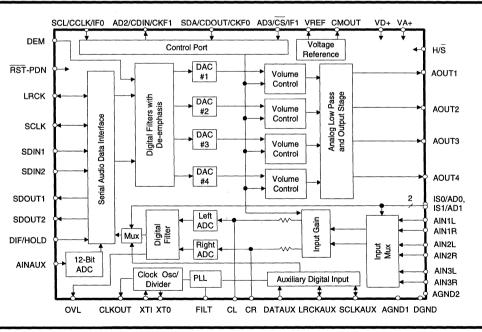

|    | - CS4303 107 dB, D/A Converter for Digital Audio                                                         |   |   |   |   |   |   |   | 8-7  |

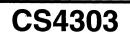

|    | - CS4328 18-Bit, Stereo D/A Converter for Digital Audio                                                  |   |   |   |   |   |   |   | 8-8  |

|    | - CS4330/1/3 8-Pin, Stereo D/A Converters for Digital Audio                                              |   |   |   |   |   |   |   | 8-9  |

|    | - CS5330/1 8-Pin, Stereo A/D Converters for Digital Audio                                                |   |   |   |   |   |   |   | 8-10 |

|    | - CS5336/8/9 16-Bit, Stereo A/D Converters for Digital Audio .                                           |   |   |   |   |   |   |   | 8-11 |

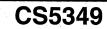

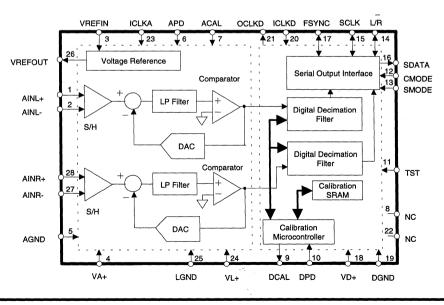

|    | - CS5349 Single Supply, Stereo A/D Converter for Digital Audio                                           |   |   |   |   |   |   |   | 8-12 |

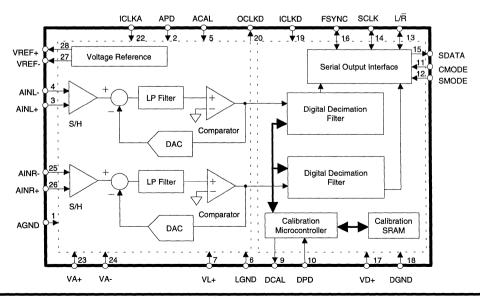

|    | - CS5389 18-Bit, Stereo A/D Converter for Digital Audio                                                  |   |   |   |   |   |   |   | 8-13 |

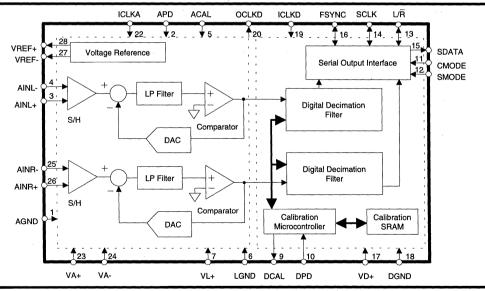

|    | - CS5390 20-Bit, Stereo A/D Converter for Digital Audio                                                  |   |   |   |   |   |   |   | 8-14 |

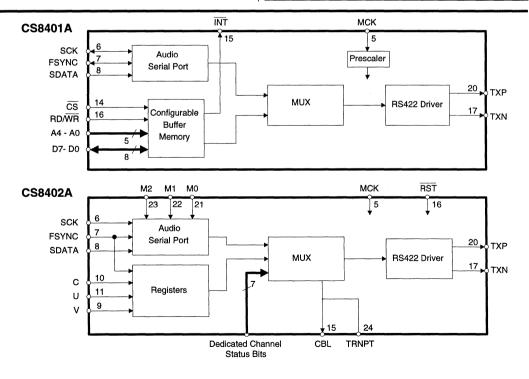

|    | - CS8401A/2A Digital Audio Interface Transmitter                                                         |   |   |   |   |   |   |   | 8-15 |

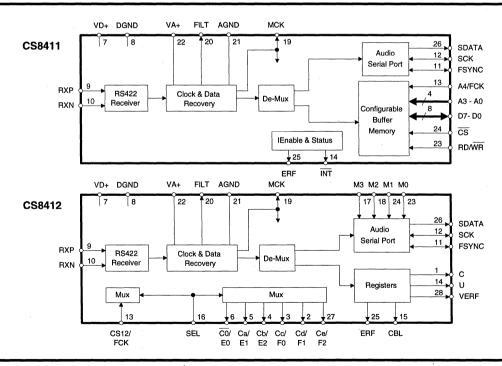

|    | - CS8411/12 Digital Audio Interface Receiver                                                             |   |   |   |   |   |   |   |      |

|    | - CS8425 A-LAN - Audio Local Area Network Transceiver                                                    |   |   |   |   |   |   |   | 8-17 |

|    |                                                                                                          |   |   |   |   |   |   |   |      |

| 9. | DATA ACQUISITION                                                                                         |   |   |   |   |   |   |   |      |

|    | - Introduction and Contents                                                                              |   |   |   |   |   |   |   | 9-2  |

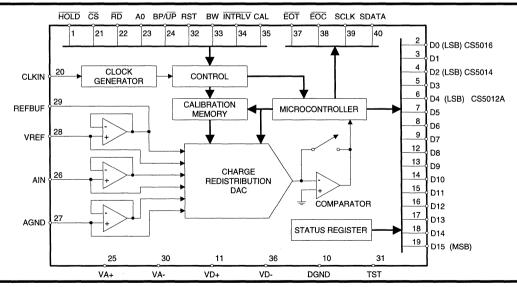

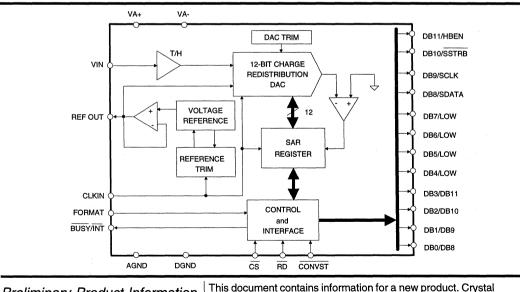

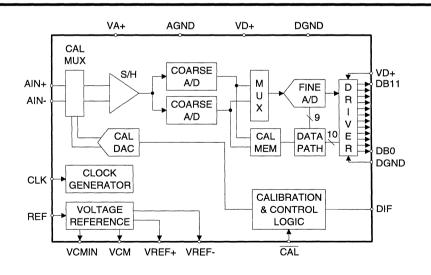

|    | - CS5012A/4/6 16, 14, & 12-Bit, Self-Calibrating A/D Converters                                          |   |   |   |   |   |   |   | 9-5  |

|    | - CS5030/1 12-Bit, 400 kHz, Sampling A/D Converters                                                      |   |   |   |   |   |   |   | 9-6  |

|    | - CS5032 12-Bit, 500 kHz, Sampling A/.D Converter                                                        |   |   |   |   |   |   |   | 9-7  |

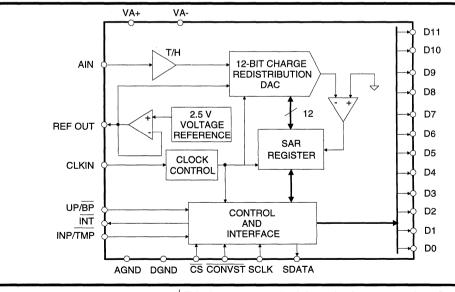

|    | - CS5101A/2A 16-Bit, 100 kHz/20 kHz A/D Converters                                                       |   |   |   |   |   |   |   | 9-8  |

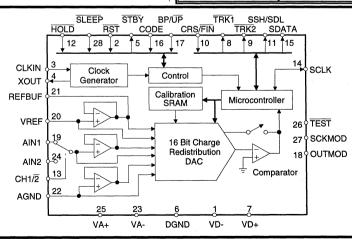

|    | - CS5317 16-Bit, 20 kHz Oversampling A/D Converter                                                       |   |   |   |   |   |   |   | 9-9  |

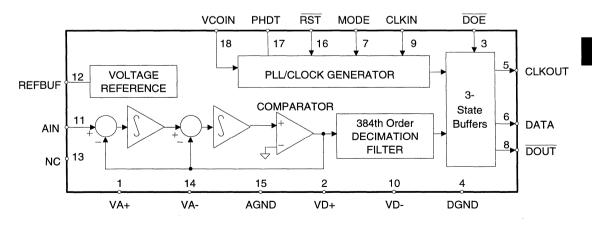

|    | - CS5321 High Dynamic Range Delta-Sigma Modulator                                                        |   |   |   |   |   |   |   | 9-10 |

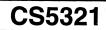

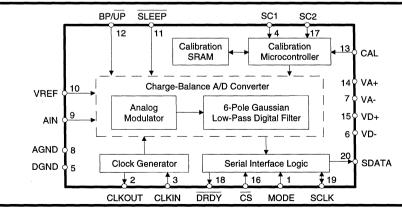

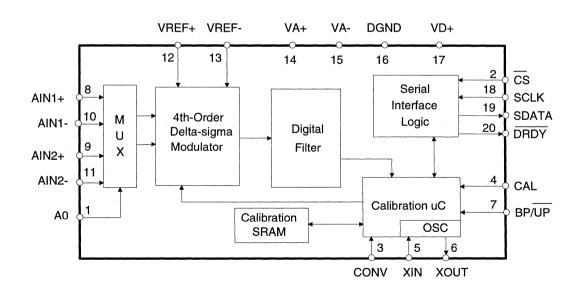

|    | - CS5322/3 24-Bit, Variable Bandwidth A/D Converters                                                     |   |   |   |   |   |   |   | 9-11 |

|    | - CS5324 120 dB, 500 Hz Oversampling A/D Converter                                                       |   |   |   |   |   |   |   | 9-12 |

|    | - CS5412 12-Bit, 1 MHz, Self-Calibrating A/D Converter                                                   |   |   |   |   |   |   |   | 9-13 |

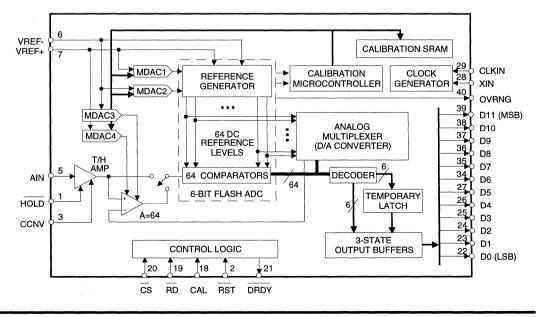

|    | - CS5480 10-Bit, 40 MHz A/D Converter                                                                    |   |   |   |   |   |   |   | 9-14 |

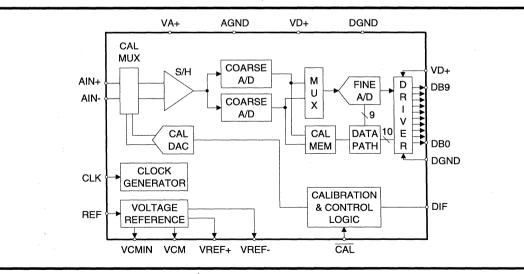

|    | - CS5490 12-Bit, 20 MHz A/D Converter                                                                    |   |   |   |   |   |   |   | 9-15 |

|    | - CS5501/3 Low-Cost, 16 & 20-Bit Measurement A/D Converters                                              |   |   |   |   |   |   |   | 9-16 |

|    | - CS5504 Low Power, 20-Bit A/D Converter                                                                 |   |   |   |   |   |   |   | 9-17 |

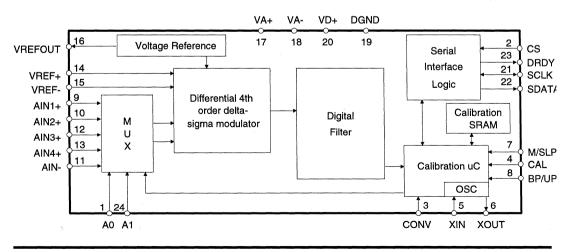

|    | - CS5505/6/7/8 Very Low Power, 16 & 20-Bit A/D Converter                                                 |   |   |   |   |   |   |   | 9-18 |

|    | - CS5509 Single Supply, 16-Bit A/D Converter                                                             |   |   |   |   |   |   |   | 9-19 |

|    | - CS5516/20 16-Bit/20-Bit Bridge Transducer A/D Converters                                               | • | • | • | • | • | • | • |      |

|    |                                                                                                          |   |   |   |   |   |   |   |      |

|    | - CS7870/5 12-Bit, 100 kHz, Sampling A/D Converters CDBCAPTURE Data Capture and Interface Board for a PC | • | • | · | • | • | • | · | 9-22 |

|    | esserie reites suit cupture une interrate sould foi u i e                                                | • | • | • | • | • | • | • | /    |

CRYSTAL

| 10. | MULTIMEDIA AUDIO PRODUCTS                                              |                                                                                      |

|-----|------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

|     | - Introduction and Contents                                            | 10-2                                                                                 |

|     | - CS4215 16-Bit, Multimedia Audio Codec                                | 10-4                                                                                 |

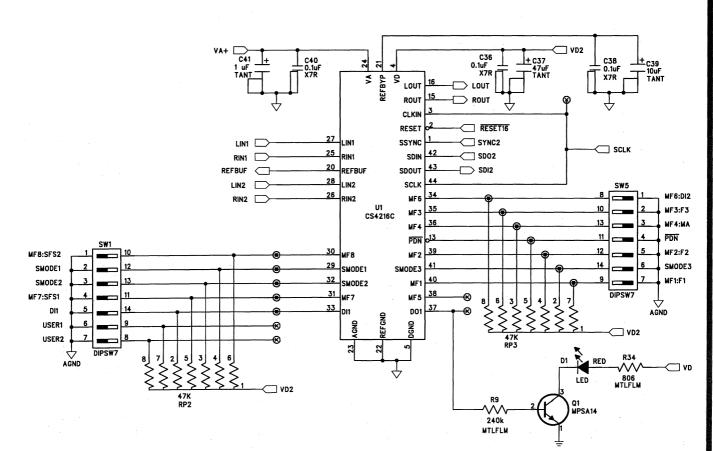

|     | - CS4216 16-Bit, Stereo Audio Codec                                    | 10-5                                                                                 |

|     | - CS4231 Parallel Interface, Multimedia Audio Codec                    | 10-6                                                                                 |

|     | - CS4231A Parallel Interface, Multimedia Audio Codec                   | 10-7                                                                                 |

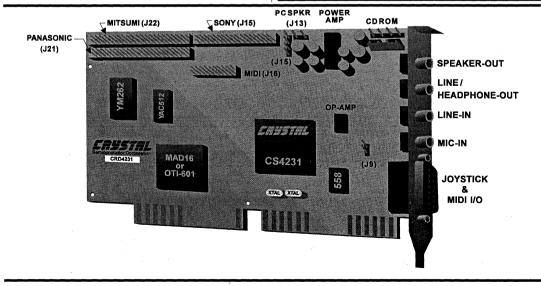

|     | - CRD4231 16-Bit, Audio Adapter Reference Design                       | 10-8                                                                                 |

|     | - CS4248 Parallel Interface, Multimedia Audio Codec                    | 10-9                                                                                 |

|     | - DRIVERS CS4231 and CS4248 Device Drivers                             | 10-10                                                                                |

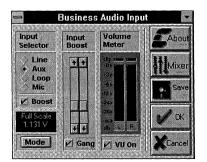

|     | - DIAGNOSTICS Multimedia Audio Codec Diagnostic Software               | 10-11                                                                                |

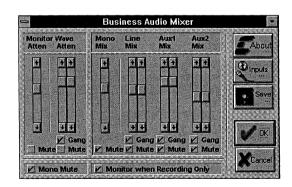

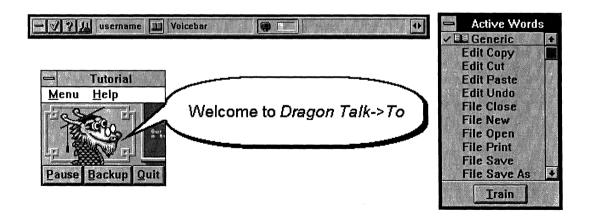

|     | - CWDRGNTT Talk $\rightarrow$ To Voice Recognition from Dragon Systems | 10-12                                                                                |

|     | - CWMNLG First Byte's Monologue for Windows                            | 10-12                                                                                |

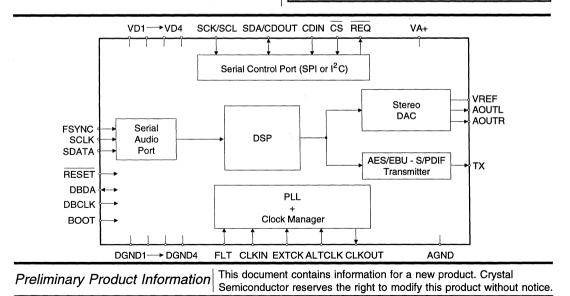

|     | - CS4920 Multi-Standard Audio Decoder - DAC                            | 10-14                                                                                |

|     | - CS8905 Programmable Music Processor                                  | 10-14                                                                                |

|     | - CS9203 Advanced Music Synthesizer                                    | 10-15                                                                                |

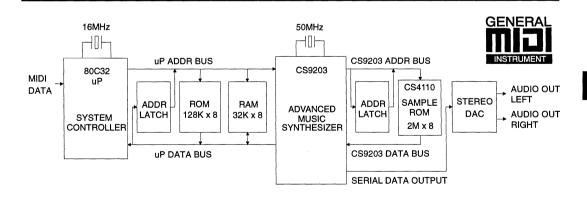

|     | - CRD9203 General MIDI Music Synthesizer Daughtercard                  | 10-10                                                                                |

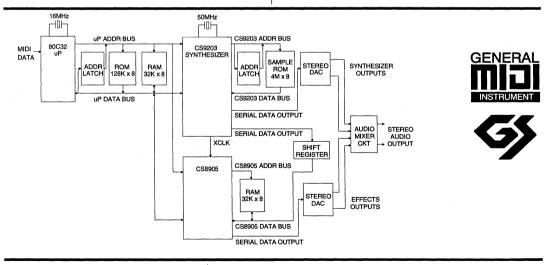

|     | - CRD9203R GM/GS Music Synthesizer Daughtercard                        | 10-17                                                                                |

|     |                                                                        | 10-10                                                                                |

|     | APPLICATION NOTES         - Contents                                   | 11-2<br>11-3<br>11-15<br>11-23<br>11-37<br>11-57<br>11-61<br>11-65<br>11-67<br>11-73 |

| 12. | APPENDICES                                                             |                                                                                      |

|     | - Contents                                                             | 12-2                                                                                 |

|     | - Product Category Levels                                              | 12-3                                                                                 |

|     | - Definition of Data Sheet Types                                       | 12-4                                                                                 |

|     | - Radiation Performance                                                | 12-4                                                                                 |

|     | - Reliability Methods                                                  | 12-5                                                                                 |

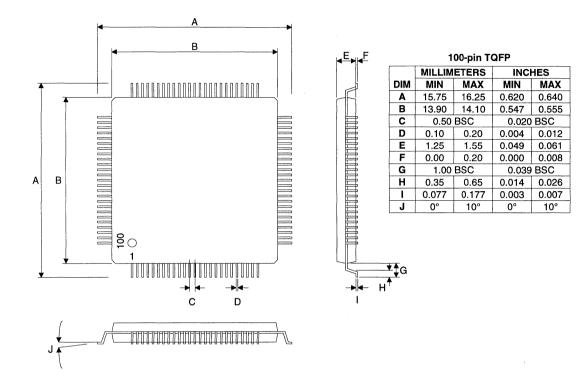

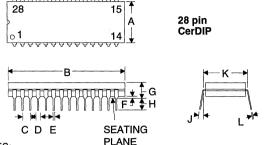

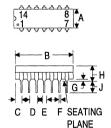

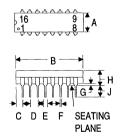

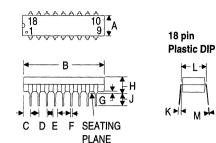

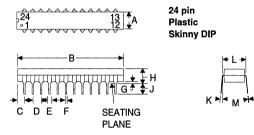

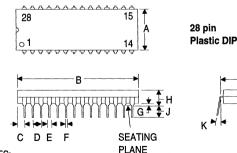

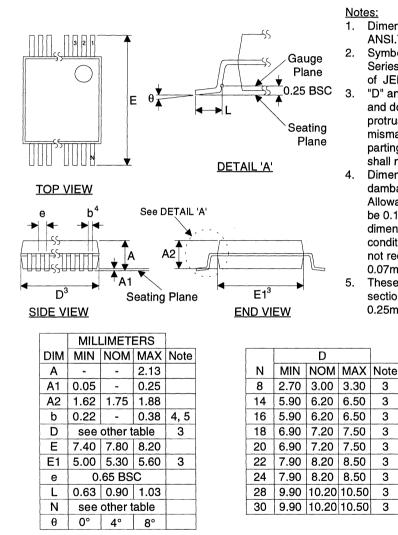

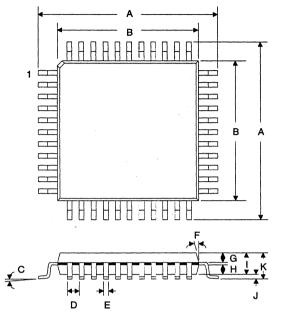

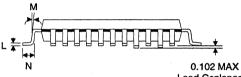

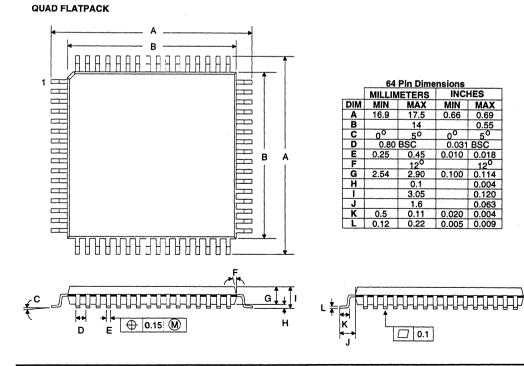

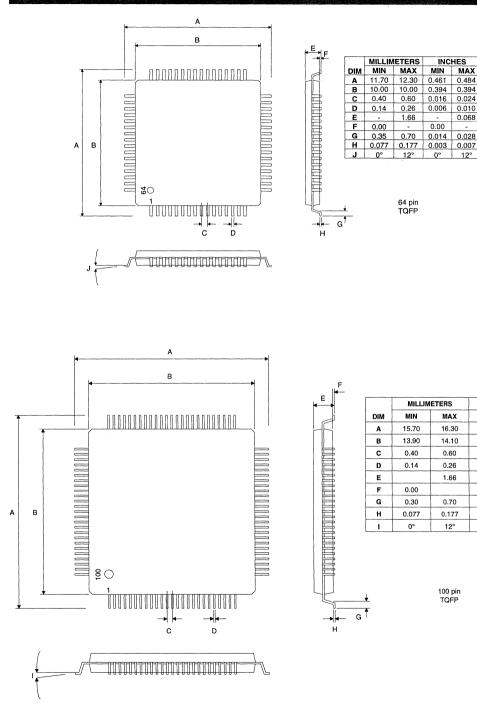

|     | - Package Outlines                                                     | 12-12                                                                                |

|     |                                                                        |                                                                                      |

| 13. | SALES OFFICES                                                          |                                                                                      |

|     | - Contents                                                             | 13-2                                                                                 |

|     | - Sales Offices                                                        | 13-3                                                                                 |

|     |                                                                        |                                                                                      |

| · · · · · · · · · · · · · · · · · · · | GENERAL INFORMATION                                                                                                | 1  |

|---------------------------------------|--------------------------------------------------------------------------------------------------------------------|----|

| LAN:                                  | ETHERNET PRODUCTS<br>10 Base-T ISA Controller<br>Ethernet/Cheapernet Transceiver                                   | 2  |

| TELECOM:                              | T1 / E1 PRODUCTS<br>T1 Framers<br>T1/E1 Line Interface ICs<br>Quartz Crystals                                      | 3  |

|                                       | JITTER ATTENUATORS                                                                                                 | 4  |

|                                       | DTMF RECEIVER                                                                                                      | 5  |

| SIGNAL PROCESSING:                    | VOICEBAND & BASEBAND PRODUCTS<br>Echo Cancellers<br>TDMA Baseband Cellular CODEC<br>Modem / Audio Analog Front-end | 6  |

| DATACOM:                              | INFRARED TRANSCEIVER                                                                                               | 7  |

| OTHER PRODUCTS:                       | CONSUMER AUDIO PRODUCTS                                                                                            | 8  |

|                                       | DATA ACQUISITION PRODUCTS                                                                                          | 9  |

|                                       | MULTIMEDIA AUDIO PRODUCTS                                                                                          | 10 |

| MISCELLANEOUS:                        | APPLICATION NOTES                                                                                                  | 11 |

|                                       | APPENDICES<br>Reliability Calculation Methods<br>Package Mechanical Drawings                                       | 12 |

|                                       | SALES OFFICES                                                                                                      | 13 |

## CONTENTS

| Product Overview                                  | 1-3  |

|---------------------------------------------------|------|

| Company Information and Part Numbering Convention | 1-9  |

| Quality and Reliability Information               | 1-11 |

8 I. I.

### AUDIO

## 1

### **Consumer and Professional Audio Products**

Crystal Semiconductor pioneered and brought delta-sigma conversion technology to production in a variety of digital audio A/D and D/A converter products. These products span the full range of price-performance requirements, from professional (e.g.,  $\geq 107$  dB ICs, the CS5390 ADC and CS4303 DAC) to consumer (e.g., 8-pin, 16-bit, stereo DAC, the CS4330).

| Products: | For data sheets, | call (512) 445-7222 |

|-----------|------------------|---------------------|

|           | ,                |                     |

Volume Control

CS3310 - Stereo, digital volume control (110 dB SNR)

#### DAC

CS4225 - Digital audio conversion system

CS4303 - 107 dB, stereo, 18-bit DAC

CS4328 - Stereo, 18-bit, delta-sigma DAC

CS4330/1/3 - stereo, delta-sigma DAC, single +5V

#### ADC

CS5330/1 - 96 dB, single +5V, stereo, 18-bit ADC (lowest power: 100 mW)

CS5336/8/9 - 95 dB, stereo, 16-bit, ADC

CS5349 - 90 dB, single +5V, stereo, 16-bit ADC

CS5389 - 107 dB, stereo, 18-bit delta-sigma ADC

CS5390 - 110 dB, stereo, 20-bit delta-sigma ADC

#### Digital Interface

CS8401A/2A - Digital audio interface transmitter (supports AES/EBU, IEC958, S/PDIF, EIAJ CP-340 formats)

CS8411/12 - Digital audio interface receiver (supports AES/EBU, IEC958, S/PDIF, EIAJ CP-340 formats)

CS8425 - 'A-LAN' Audio Local Area Network transceiver (I2C bus, parallel interface, or stand-alone transceiver)

#### Multimedia Audio Products

Crystal Semiconductor's pioneering work in mixed-signal integration has brought low-cost, stereo, 16-bit A/D and D/A conversion to the world of computer multimedia. Crystal's 16-bit solutions have been established as the industry standard, and cost less than traditional 8-bit alternatives.

Crystal's multimedia codecs achieve new levels of integration by combining CD-quality 16-bit converters, anti-aliasing filters, smoothing filters, and programmable gain and volume control on a single chip. The core converters are based on Crystal's proprietary delta-sigma techniques.

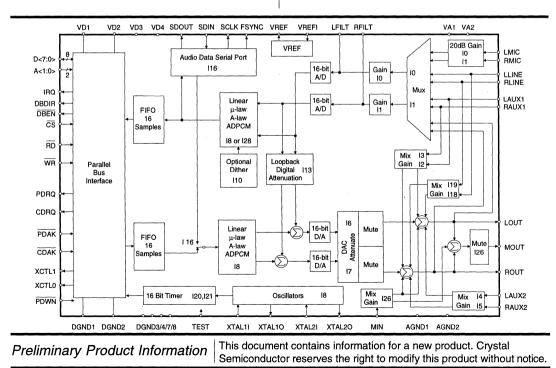

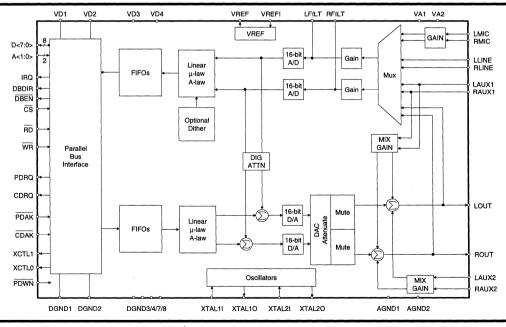

Both the CS4248 and the CS4231 integrate the PC ISA bus interface on-chip, as well as analog and digital mixers. The CS4231 includes a variety of enhanced features such as added mixing and on-chip ADPCM compression.

#### Products: For data sheets, call (512) 445-7222

Audio Codec

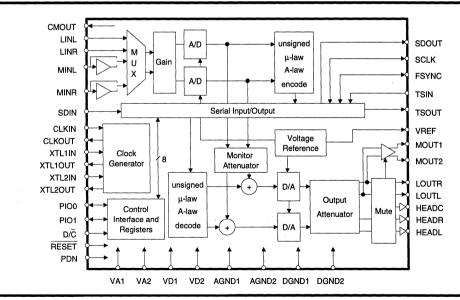

- CS4215-Multimedia codec, stereo 16-bit A/D and D/A, microphone gain, headphone driver, A-law/m-law option.

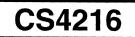

- CS4216 -Multimedia codec, stereo 16-bit A/D and D/A programmable input gain and output volume control

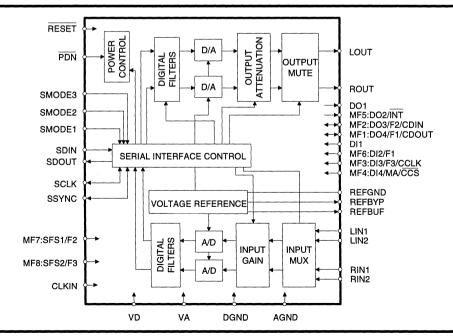

- CS4231/31A Parallel (ISA/EISA) interface multimedia codec, stereo, 16-bit A/D and D/As,ADPCM, MPC mixer, on-chip FIFOs, full-duplex operation, 16-mA bus driver; pin-compatible upgrade to CS4248.

- CS4248 Parallel (ISA/EISA) interface multimedia codec,stereo, 16-bit A/D and D/As, on-chip FIFOs, analog- and digital-mixing capability

#### DSP Audio

CS4920 - Audio decompression with integrated stereo DAC and clock manager

#### PRODUCT OVERVIEW

#### **AUDIO**

#### Music Synthesis Products

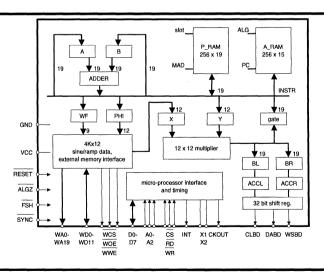

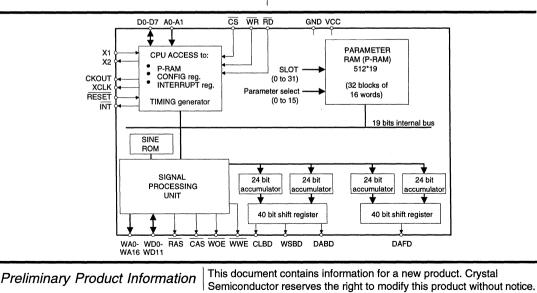

Crystal Semiconductor offers two high-performance wavetable music synthesizer products. These digital signal processor (DSP)-based devices offer sound-generation capabilities typically found only in professional-quality keyboards and electric pianos. The CS8905 and CS9203 are ideal for applications such as music keyboards, karaoke equipment, arcade games, MIDI sound modules and personal computer (PC) add-in boards.

Several complete system solutions are available from Crystal. First, the CS8905 may be used as a General MIDI-compatible synthesizer (16-note polyphony, 16-part multitimbral) with a 1-Mbyte wavetable sample set, suitable for cost-sensitive applications such as PC add-in boards. A highpolyphony, multi-timbral version may be implemented using the CS9203; this solution performs General MIDI-compliant music synthesis (24-note polyphony, 16 timbres), with either 2 or 4 Mbytes of wavetable sample data supplied under license by Crystal. The CS8905 can optionally be used with the CS9203 as a programmable effects processor, performing Roland<sup>®</sup> Sound Canvas (GS)-compatible reverb and chorus.

# Products: For data sheets, call (512) 445-7222

CS8905 - Programmable Music Processor

CS9203 - Advanced Music Synthesizer

CRD9203R - CS8905/9203-Based System Solution

## COMMUNICATION

#### **PRODUCT OVERVIEW**

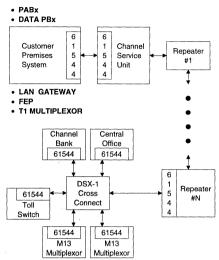

#### T1/E1 Products

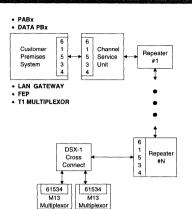

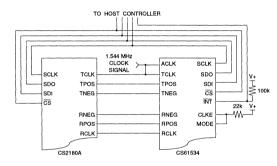

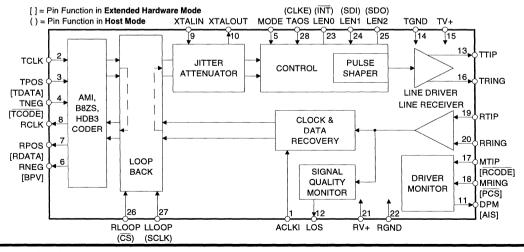

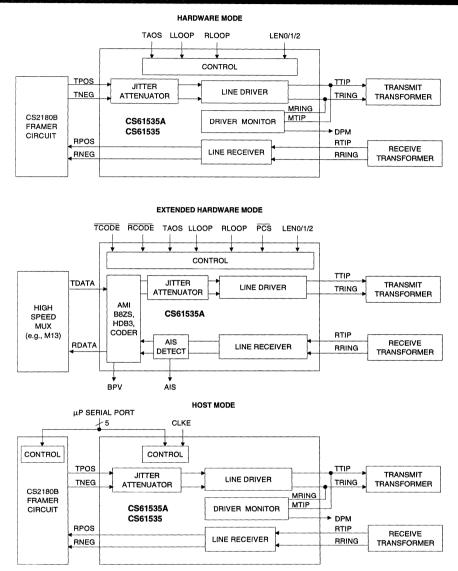

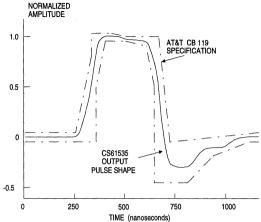

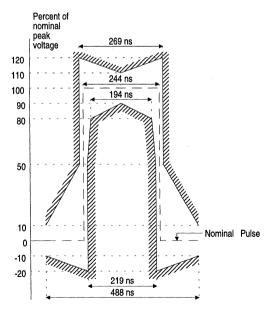

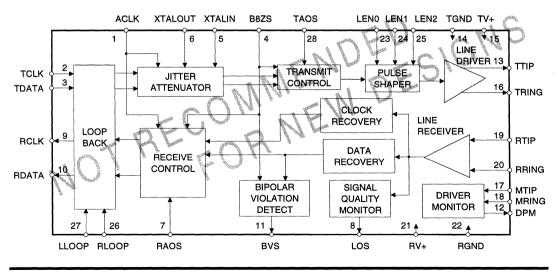

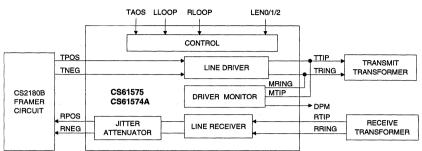

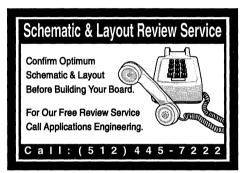

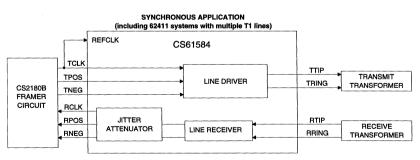

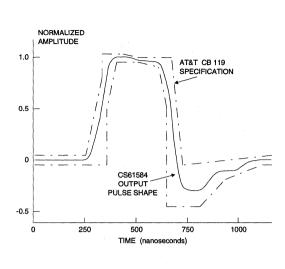

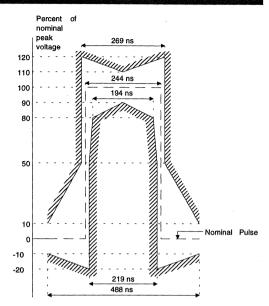

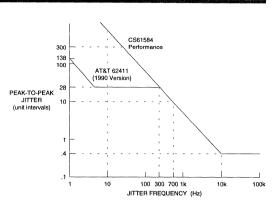

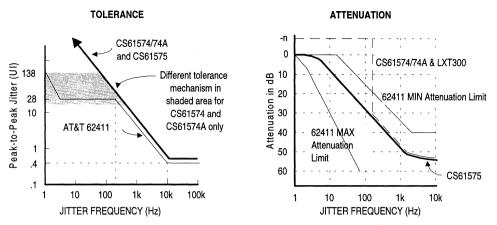

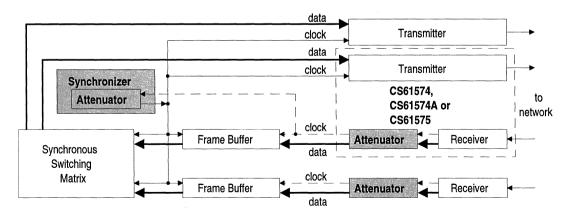

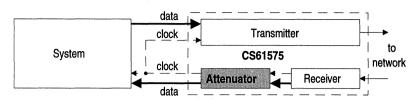

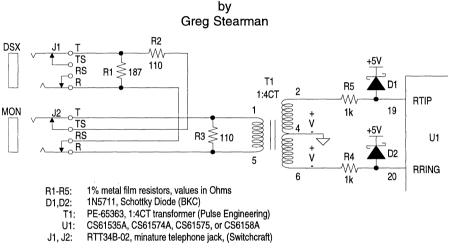

Crystal Semiconductor offers a broad family of low-power CMOS PCM line interface circuits, with each device optimized for a unique system application. The CS61535A, CS61574A, CS61575 and CS61584 are recommended for use in new designs.

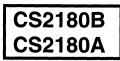

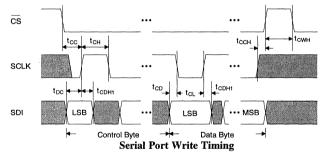

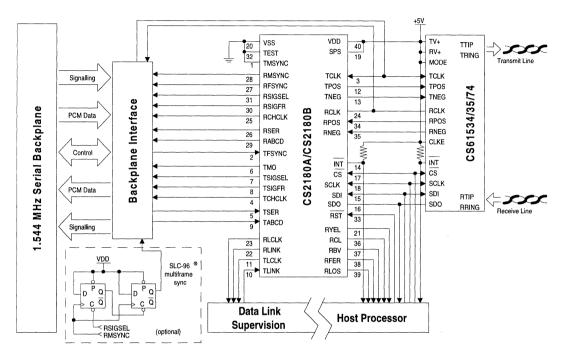

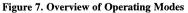

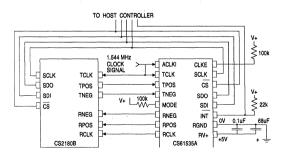

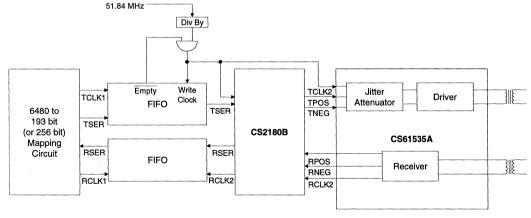

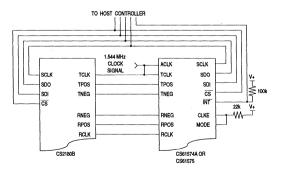

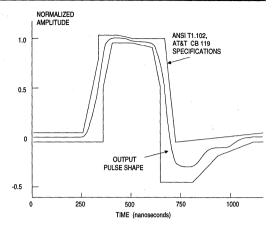

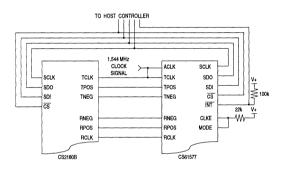

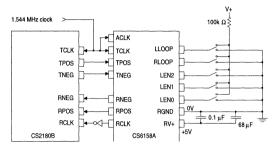

Crystal Semiconductor's leadership continues with the-best in-class: transmission-line impedance matching, short-circuit current limiting, pulse shapes, jitter attenuation, jitter tolerance and low power consumption. Our CS2180B T1 Transceiver is a perfect companion to our T1 line interface ICs. This device handles encoding and decoding of all T1 frame formats (D4, SLC96, T1DM, and ESF).

#### Products:

Datasheets are in this databook

- CS2180A/B T1 framers

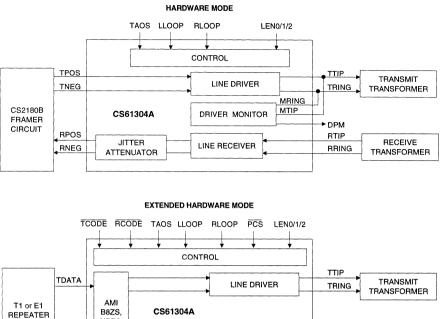

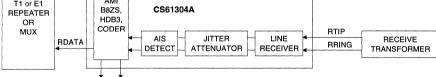

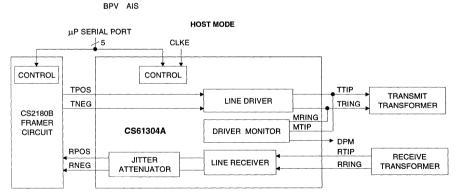

- CS61304A T1/E1 Line Interface. Enhanced, drop-in replacement for LXT304.

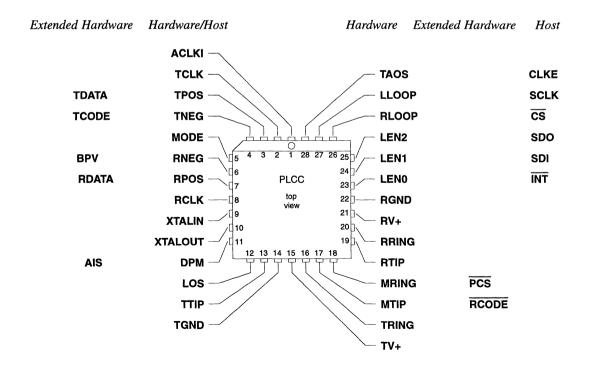

- CS61305A T1/E1 Line Interface. Enhanced, drop-in replacement for LXT305.

- CS6152 Low-power T1 Analog Line Interface for use with external clock recovery circuits

- CS61534 T1/E1 Line Interface Unit

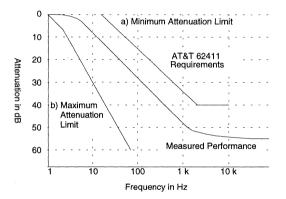

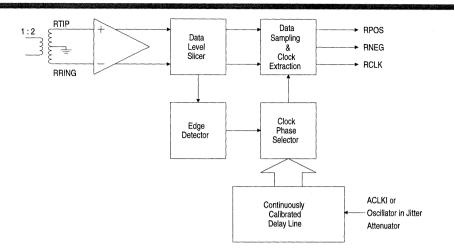

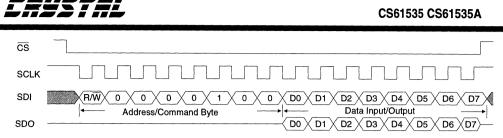

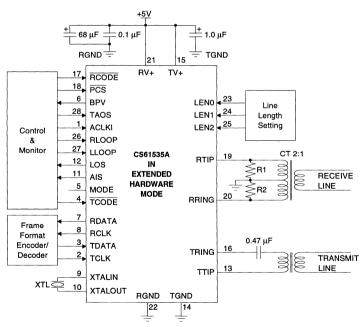

- CS61535/35A Low-power T1/E1 Line Interface with transmit-path jitter attenuation.

- CS61544 T1 Line Interface unit

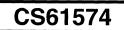

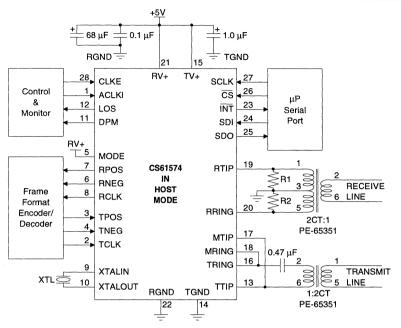

- CS61574 T1/E1 Line Interface unit

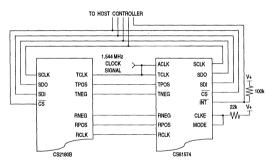

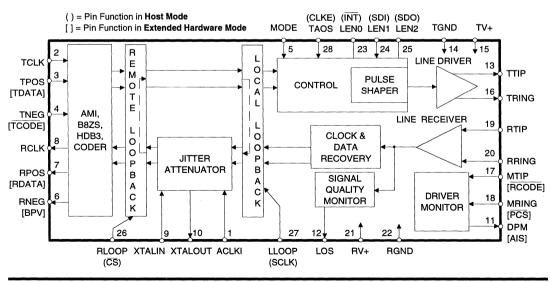

- CS61574A/75 Low-power T1/E1 Line Interface with receive-path jitter attenuation.

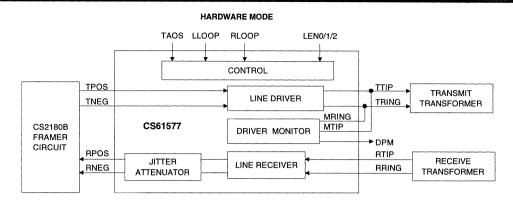

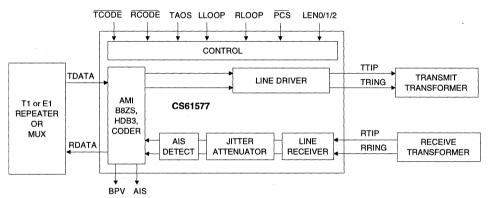

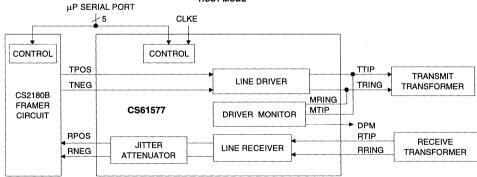

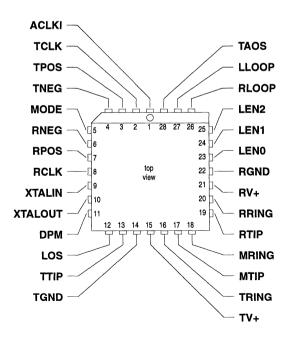

- CS61577 T1/E1 Line Interface. Enhanced, drop-in replacement for CS61574.

- CS6158/58A T1/E1 Line Interface

- CS61584 Low-power, highly-programmable, dual-channel, 3.3V & 5V, T1/E1 Line Interface

#### **DTMF** Receiver

The CS8870 DTMF receiver is compatible with industry-standard 8870 devices.

|  | Product: | Datasheet is in this data book |

|--|----------|--------------------------------|

|--|----------|--------------------------------|

CS8870 - DTMF Receiver with adjustable receive sensitivity and detection/release times.

### COMMUNICATION

### **PRODUCT OVERVIEW**

#### LAN Products

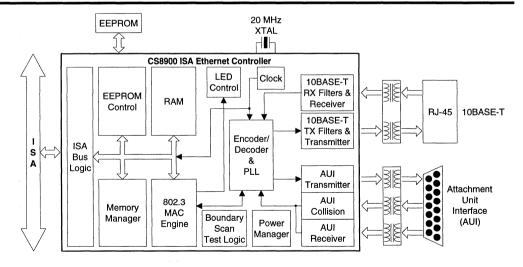

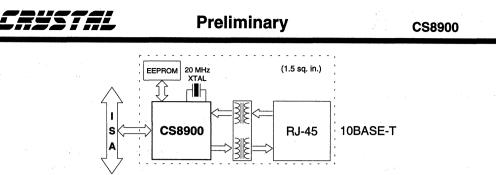

Crystal Semiconductor offers a complete Ethernet hardware solution, consisting of the CS8900 ISA-bus, 10BaseT controller (with AUI port), and the CS83C92C coaxial-cable transceiver.

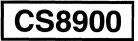

The CS8900 is a low-cost Ethernet LAN Controller optimized for ISA Personal computers. Its highly-integrated design eliminates the need for costly external components required by other Ethernet controllers. The CS8900 includes onchip RAM, 10Base-T transmit and receive filters, and a no-glue ISA-Bus interface with 24 mA drivers.

The CS8900's patented PacketPage<sup>TM</sup> architecture automatically adapts to changing network traffic patterns and available system resources. the result is increased system efficiency and minimized CPU overhead.

Crystal is the first company to bring the benefits of low-power CMOS technology to Ethernet/Cheapernet transceivers. The CS83C92C uses up to 40 percent less power than the DP8392A and DP8392B. This translates into increased reliability and compatibility with surface-mount technology. The CS83C92C is the first Ethernet transceiver that is fully compliant with ISO/IEEE 802.3.

Products: Datasheets are in this databook.

CS8900 -ISA-bus Ethernet Network Interface Controller

CS83C92A/C - IEEE 802.3-compatible CMOS coaxial transceiver interface

#### Voiceband & Baseband Products

Crystal Semiconductor offers a broad variety of technology for processing voiceband and radio baseband signals. The CS645x series of products are representative of Crystal's ability to apply its delta-sigma converter technology to specific communication applications. Crystal will develop custom codec circuits for high-volume applications.

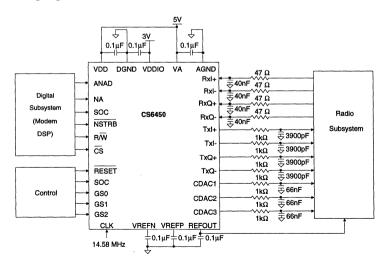

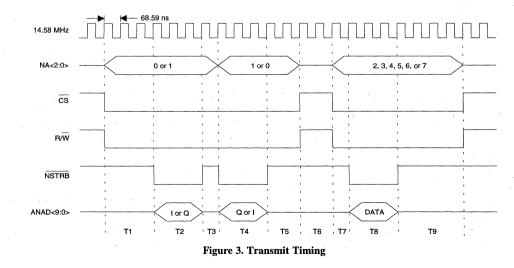

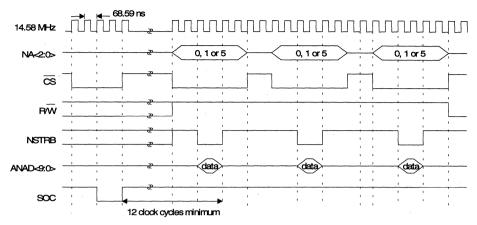

The CS6450 supports CDPD and TDMA cellular phones, and provides a baseband interface between a DSP and a radio module.

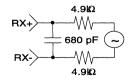

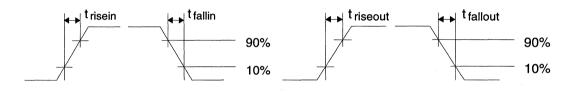

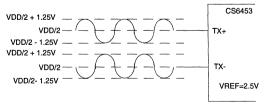

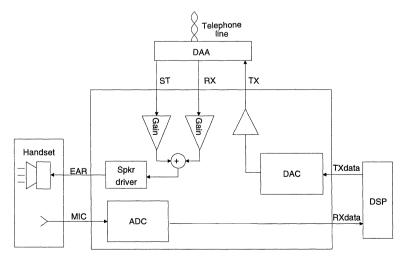

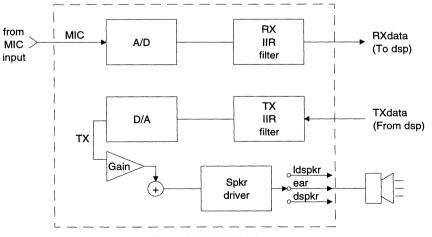

The CS6453 supports high-performance modems, and provides a voiceband interface between a DSP and a direct access arrangement.

| Products: | Datasheets | are in | this da | atabook. |

|-----------|------------|--------|---------|----------|

|           |            |        |         |          |

CS6450 - I&Q Baseband codec for AMPS/TDMA/CDPD applications

CS6453 - Low-cost, single-channel, alternating voice/data codec for V.34/V.17 modem applications

## COMMUNICATION

#### Personal Communication

Crystal Semiconductor is a leading supplier of mixed-signal technology to the new and emerging Personal Digital Assistant and personal communications marketplaces, offering both standard off-the-shelf, and custom/customer specific integrated circuits.

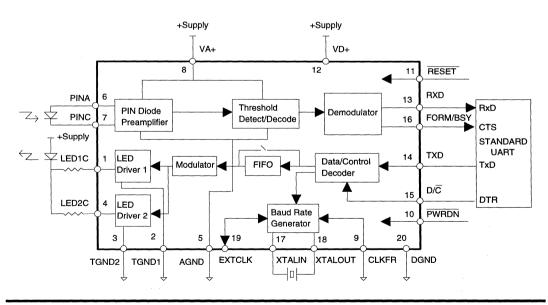

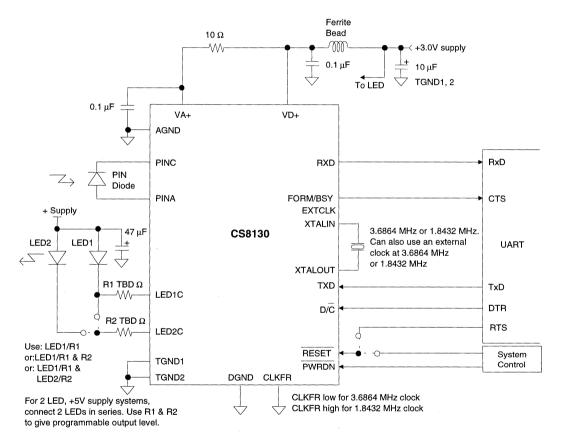

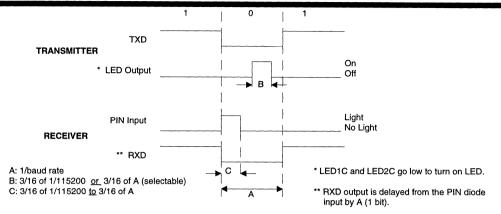

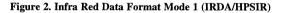

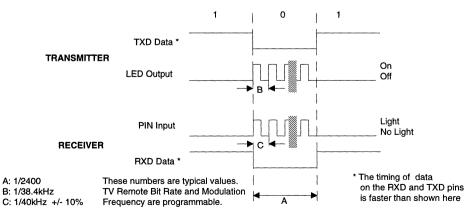

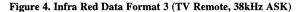

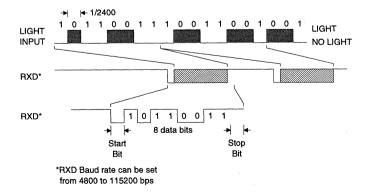

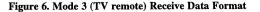

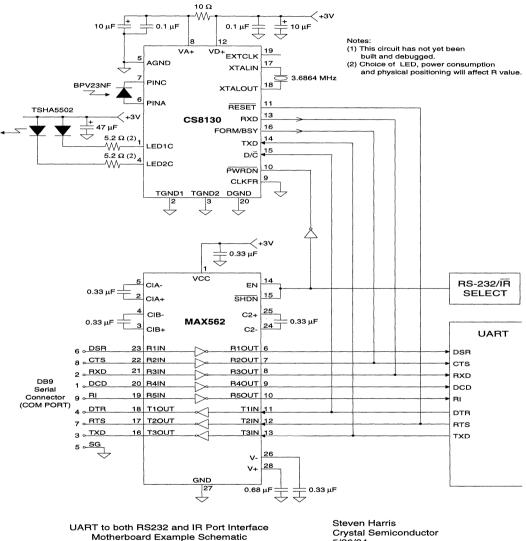

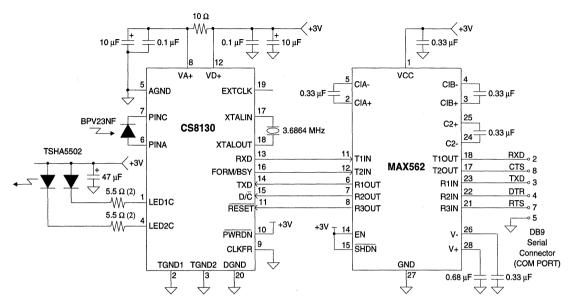

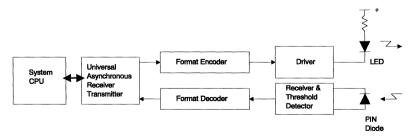

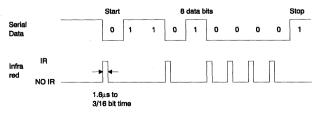

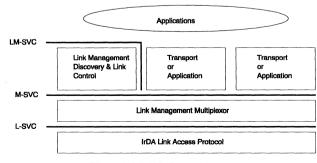

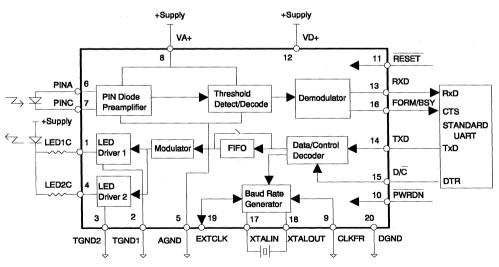

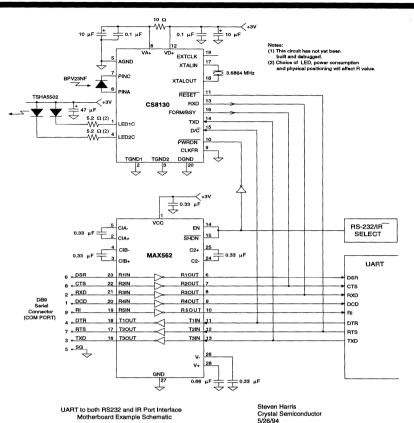

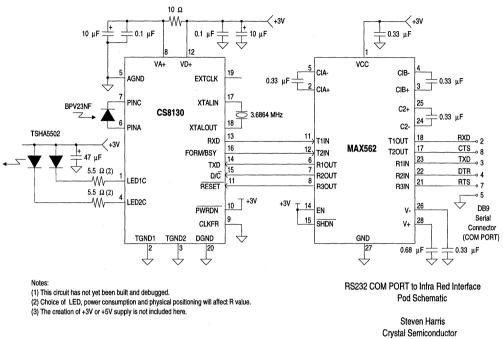

Crystal's first standard product is the CS8130 Multi-Standard Infrared Transceiver. The CS8130 adds an IR port to a standard UART, and implements the IrDA physical-layer. Other standards supported are HP-SIR, ASK and TV remote. The computer data port is standard UART TxD and RxD compatible, and operates from 1200 to 115200 baud. The CS8130 uses an external PIN diode and transmit LED.

Crystal's technology portfolio includes all of the building blocks required for PDA mixed-signal controllers. These technologies include audio codecs, radio baseband codecs, screen digitizers, clock generators, phase-lock loops, and DCmeasurement ADCs. Crystal will design custom PDA controllers for high-volume opportunities.

Products:

Datasheets are in this databook.

CS8130 -Multi-Standard infrared transceiver for IrDA, HPSIR, ASK and TV-remote applications.

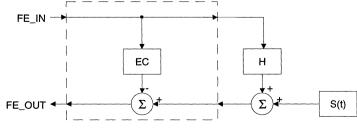

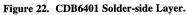

#### Echo Cancellation

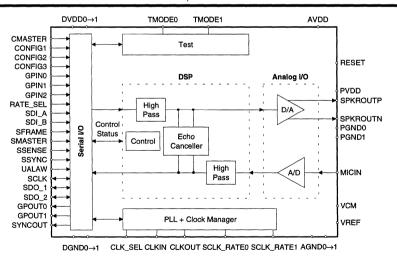

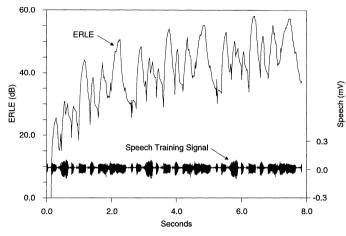

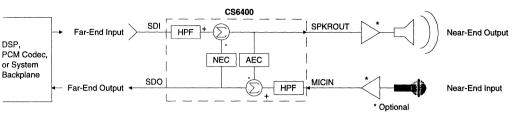

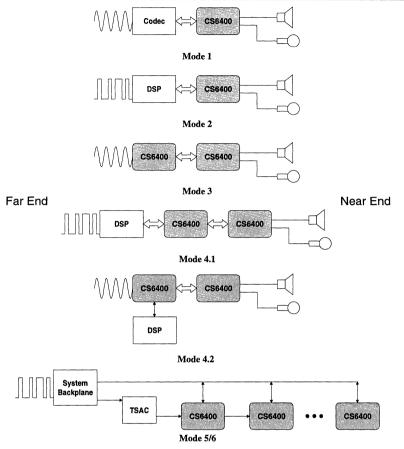

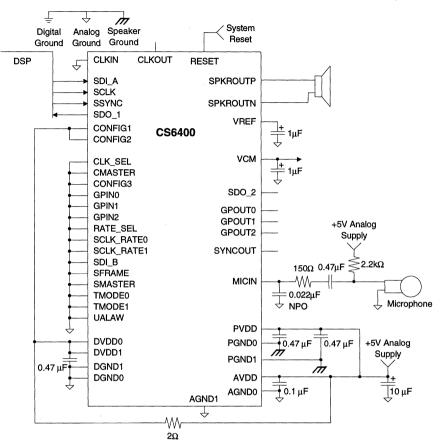

The CS6400 and CS6401 are voiceband echo cancellation products which can be used in fullduplex speakerphones, cellular phones, base stations, personal digital assistants, video-teleconferencing and long-distance telephone lines. These circuit contain embedded, low-cost, application-specific DSPs, and can cancel up to 64 ms of acoustic or network echo.

PRODUCT OVERVIEW

| Products: | Datasheets are in this databook.                                            |

|-----------|-----------------------------------------------------------------------------|

|           | Low-cost, echo-canceling codec with rated DSP, linear codec, and program I. |

|           | Programmable echo-canceller, with nal program ROM.                          |

#### DATA ACQUISTION

#### General Purpose A/D Converters

Crystal's general-purpose ADCs are more accurate and stable than any previously available. Traditional data converters required regular equipment calibration by service technicians to adjust for drift in analog components. Integrated digital correction architectures make Crystal's SMARTAnalog products self-calibrating, dramatically reducing maintenance requirements. For example, the CS5030 has a Total Unadjusted Error of  $\pm 1$  LSB and a reference tempco of 1ppm/°C over the -55° C to 125°C temperature range.

| Products: | For data sheets, call (512) 445-7222                 |

|-----------|------------------------------------------------------|

|           | A/4/6 - 12/14/16-bit, self-calibrating<br>converters |

|           | 1 - 12-bit, 500 kHz absolute-accurate<br>converters  |

| CS5032-   | 12-bit, 500 kHz A/D converter                        |

|           | A/2A - 16-bit, 100/20-kHz sampling<br>) converters   |

|           | - 16-bit, 20 kHz oversampling A/D verter             |

| CS5412    | - 12-bit, 1 MHz A/D converter                        |

| CS5480    | - 10-bit, 40 MHz A/D converter                       |

- CS5490 12-bit, 20 MHz A/D converter

- CS7870/5 12-bit, 100 kHz sampling A/D converters

#### Measurement A/D Converters

Low-frequency measurement devices based on 'delta-sigma' architectures are a new type of pioneered ADCs by Crystal. These SMARTAnalog devices combine data conversion with on-chip digital signal processing to perform sophisticated filtering of the analog input. The result is a single device that replaces a significant amount of expensive discrete analog glue circuitry used for signal conditioning. Manufacturers of industrial data-acquisition systems are saving money by using a separate measurement ADC for each analog input channel. Previously, such systems would have used a single veryhigh-speed ADC centralized to process many input channels.

| Products: | For data sheets, call (512) 445-7222                  |

|-----------|-------------------------------------------------------|

|           | - High-dynamic-range delta-sigma<br>dulator           |

| 000022    | /23 - 24-bit variable bandwidth A/D<br>werter chipset |

| CS5324    | - 120 dB A/D converter                                |

|           | /3 - 16/20-bit, measurement A/D<br>averter            |

| CS5504    | - 20-bit, two-channel A/D converter                   |

| CS5505    | /6/7/8 - 16/20-bit, A/D converters                    |

| CS5509    | - 16-bit, low-cost A/D converter                      |

|           | /20 - 16/20-bit, bridge transducer A/D<br>averter     |

|           |                                                       |

# **COMPANY INFORMATION**

Crystal's proprietary SMART Analog<sup>™</sup> design technique, incorporating analog and digital circuitry in monolithic CMOS devices, represents a powerful new technology in the semiconductor industry. This innovative approach to design eliminates many of the sources of inconsistent performance in traditional analog circuitry.

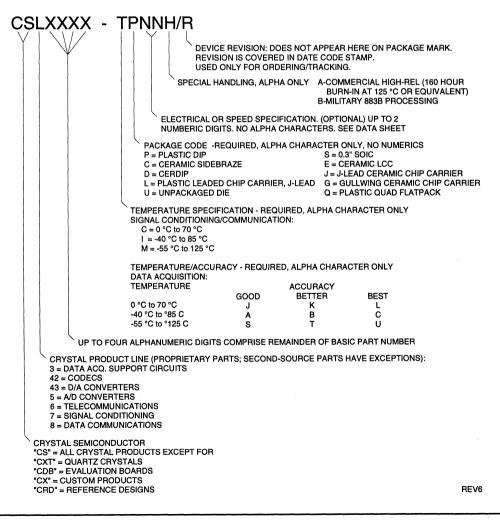

Maximum system performance is built-in from initial research on end-user requirements through product definition. Product quality and reliability is designed into the device architecture and is further assured through rigorous standards for fabrication, assembly and testing. Crystal's part numbering scheme is as follows:

I

CRYSTAL

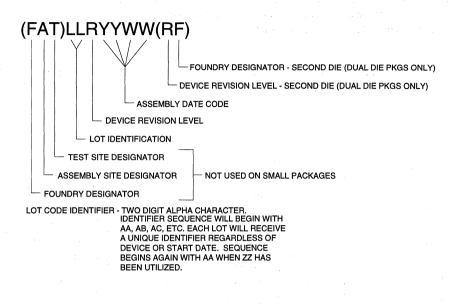

In addition to the part number, all Crystal parts have a second line of marking, which can be decoded as follows:

#### COMPANY BACKGROUND

Crystal Semiconductor Corporation was founded in 1984 with the goal of supplying the industry with high-performance, mixed analog/digital CMOS circuits. In 1991, Crystal became a wholly owned subsidiary of Cirrus Logic.

To meet its objectives, Crystal recruited a staff of renowned CMOS analog design engineers, a scarce resource in the industry, and teamed them with designers trained in system architecture development.

By coupling this design staff with highly qualified application and test engineers and seasoned management, Crystal has achieved several industry firsts. Systems designers now benefit from the performance and cost savings of Crystal breakthroughs such as self-calibrating ADCs, monolithic T1 interfaces and the industry's first implementations of "delta sigma" oversampling A-to-D converters.

Headquartered in Austin, Texas, Crystal sells its products worldwide through a network of manufacturer's representatives. Crystal's entire marketing and sales organization is committed to providing quality products and reliable, rapid service.

Crystal Semiconductor is committed at every level of the company to the highest possible standards of quality and reliability in its products. This commitment is evident in all phases of operations: initial product definition, design, fabrication, assembly, test, qualification and customer service. Product quality and reliability are active concerns of each Crystal employee. Quality is ingrained in every operation throughout the product life cycle. Some of the key operations are discussed below.

#### In Product Definition

To ensure maximum system performance, Crystal works with users to identify and quantify the parameters, including quality and reliability issues, that best serve customer needs. Quality and reliability become part of the design goals, along with electrical performance and cost.

#### In Design

Conservative CMOS design rules are the basis for all current Crystal products. In addition, extensive use is made of proven standard cells to drastically reduce the possibility of design errors.

Each pin in every SMART Analog product is designed to meet ESD levels of at least 2500V when tested per MIL STD 883, Method 3015. Each pin is also designed to withstand more than 200mA of DC latch current.

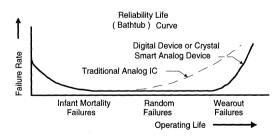

Crystal SMART Analog design architectures provide quality and reliability comparable to leading digital devices and memories. This is far superior to traditional analog ICs and hybrids. On-chip digital error correction provides stable performance over time and temperature by taking advantage of digital controls that are insensitive to parametric analog problems such as leakages and shifts in threshold voltage. Using Crystal devices, designers have fewer error sources to consider. The result is a less complicated, more reliable system.

#### In Fabrication and Assembly

Crystal ensures reliable delivery of quality parts by accessing established foundries in multiple locations worldwide. Each fabrication facility is qualified by Crystal. Assembly is performed both domestically and offshore under carefully documented and well-controlled conditions.

Wafer fabrication and assembly processes undergo in-line quality inspections. Wafers are inspected optically to guidelines based on MIL STD 883, Method 2010, Class B. Each die is electrically tested using proprietary test circuits that verify key parameters. Following assembly, packages are subjected to a variety of mechanical inspections to verify integrity and insure high quality. (For example, x-ray inspection to 3.0 percent LTPD is one of the standard production tests.)

#### In Test

In a break from traditional analog components, Crystal's SMART Analog products include basic test capabilities designed into each chip. Crystal's in-process quality assurance program uses this designed-in testability to monitor and track the performance and quality of these complex circuits. Finished packaged components are tested 100 percent electrically, over temperature where critical parameters are involved. With these extensive quality programs, Crystal guarantees outgoing electrical quality levels on all data sheet specifications to a 0.065 percent AQL level over the full specified temperature range.

Throughout the assembly and test phases, traceability to the original wafer lot is carefully maintained.

#### In Product Qualification

Before any Crystal product is released to production and shipped in volume, it must undergo a thorough qualification program. Crystal has separate qualification criteria to address both longterm reliability and infant mortality so that the sources of failure are identified and eliminated. Crystal uses military specifications as the guidelines for reliability tests, methods and procedures. (See Qualification Criteria Table)

To ensure reliability of the design and processes, full qualification requires that three non-consecutive lots are used during the qualification program. Fabrication and assembly facilities are audited every six months and routinely monitored. Any major design or process changes are re-qualified.

These steps guarantee that Crystal products maintain the high standards of reliability designed-in from the start.

#### In Customer Service

Compliance with purchasing requirements is ensured through the use of Crystal's computerized system "Compass" (Crystal On-line Marketing, Production, and Sales System). This processing system ensures that all orders are entered correctly, scheduled properly, produced according to schedule, and shipped with zero discrepancies.

All systems and procedures at Crystal Semiconductor are aimed at continuously improving the quality and reliability of our products and services to meet the needs of our customers.

Crystal's philosophy on quality is to anticipate problems and develop systems and controls to alleviate possible problems. It is a well stated fact by Juran and Deming, two of the nation's foremost experts on quality, that 85% of all quality problems are system related and 15% are worker related. Therefore, Crystal devotes its major quality efforts toward preventing system related quality problems.

Crystal has a very aggressive audit program in place. Monthly internal audits are performed to insure compliance to the extensive documentation of instructions and criteria for testing and inspection. Semi-annual vendor audits are performed on the assembly and fabrication foundries. Vendor audits insure the adequacy and compliance of specifications, product flow, training, process controls and cleanliness. All internal and external audits have provisions for ratings and a system for corrective action requirements. These frequent audits by assembly, fabrication and quality engineers maximize system quality compliance.

As an added measure of continued high quality from assembly and fabrication foundries, thorough incoming inspections are performed. Wafer level optical inspection is based upon guidelines of MIL STD 883, METHOD 2010, Class B. Test die are electrically tested to verify compliance to key process parameters based upon design rule specifications. These electrical parameters include threshold voltages, breakdown voltages, material resistance, and contact resistance. Assembly packaging inspection includes external visual, marking permanency, solderability, x-ray, hermeticity, die shear, wirepull and internal visual.

Preventive measures are very much in force in the final test area. Equipment calibration and preventive maintenance procedures are strictly adhered to. Handling procedures for Electrostatic Discharge are in place throughout the test areas. Non-conforming material is segregated until disposition by a material review board. There are controlled procedures for releasing new test programs and new test equipment to the production environment. In summary, Crystal Semiconductor is committed to meet the quality requirements of its customers.

# **QUALITY AND RELIABILITY INFORMATION**

# **Qualification Criteria Table**

| Qualification Criteria Table                                      |                       |               |              | World       |                                |

|-------------------------------------------------------------------|-----------------------|---------------|--------------|-------------|--------------------------------|

|                                                                   |                       | Production    | Production   | Class       |                                |

|                                                                   | Method                | Level III     | Level II     | Level I     | <u>Units</u>                   |

| Quality Performance                                               |                       |               |              |             |                                |

| Outgoing Quality (elec./vis-mech/ship.)                           | Crystal Spec.         | 2500          | 1500         | 500         | DPM                            |

| Fault Coverage (Digital)                                          |                       | n/a           | n/a          | 95%         | %                              |

| Datasheet Test Coverage (Digital)                                 | Datasheet             | 100%          | 100%         | 100%        | %                              |

| Datasheet Test Coverage (Analog)                                  | Datasheet             | 100%          | 100%         | 100%        | %                              |

| ESD - Human Body Model                                            | MIL 3015              | 1500          | 2000         | 4000        | v                              |

| ESD - Machine Model                                               | MIL3015               |               |              | 300         | v                              |

| Latchup - Power Supply <sup>1</sup>                               | JEDEC 17              | Vcc+1V        | Vcc+50%      | Vcc+50%     | v                              |

| Latchup - I/O <sup>1</sup>                                        | JEDEC 17              | ±50           | ±100         | ±200        | mA                             |

|                                                                   |                       |               | 1100         |             |                                |

| Reliability Performance                                           |                       |               |              |             |                                |

| Infant Mortality (48hrs@125°C or equiv.) <sup>2</sup>             | MIL 1005              |               |              | 1000        | DPM                            |

| Early Life (168hrs@125°C or 1yr. equiv.) <sup>3</sup>             | MIL 1005              | 1/1674        | 500          | 300         | FITS                           |

| Operating Life (1000hrs@125°C or 10yr, equiv.) <sup>3</sup>       | MIL 1005              | 500           | 300          | 100         | FITS                           |

| Operating Life (1000118@125 C 01 1091, equiv.)                    | IVIL 1005             | 500           | 300          | 100         | FII3                           |

| Moisture Performance                                              |                       |               |              |             |                                |

| Moisture Resistance - THB (plastic pkgs)                          | JEDEC 22B             | 500/5%        | 1k/5%        | 1k/3%       | hrs/%LTPD per lot <sup>5</sup> |

| 4 I O /                                                           |                       |               |              |             |                                |

| Autoclave (plastic pkgs)                                          | JEDEC 22B             | 96/5%         | 144/5%       | 144/3%      | hrs/%LTPD per lot <sup>5</sup> |

| Mashaniaal Darformanaa                                            |                       |               |              |             |                                |

| Mechanical Performance                                            | ·                     | 500/50/       | 41./50/      | 41./00/     |                                |

| Temp Cycle (plastic pkgs)                                         | MIL 1010              | 500/5%        | 1k/5%        | 1k/3%       | #cy/%LTPD per lot <sup>5</sup> |

| Thermal Shock (plastic pkgs)                                      | MIL1011               | 200/5%        | 500/5%       | 1k/3%       | #cy/%LTPD per lot5             |

| Temp Cycle w/ Hermeticity (hermetic pkgs)                         | MIL1010/14            | 500/5%        | 1k/5%        | 1k/3%       | #cy/%LTPD per lot <sup>5</sup> |

| Thermal Shock w/ Hermeticity (hermetic pkgs)                      | MIL 1011/14           | 200/5%        | 500/5%       | 1k/3%       | #cy/%LTPD per lot <sup>5</sup> |

| Soak &VPR (surface mount plastic pkgs)                            | Crystal Spec.         | 3/5%          | 3/3%         | 3/1%        | #cy/%LTPD per lot5             |

| Xray                                                              | Crystal Spec.         | 2.50%         | 2.50%        | 0.65%       | %AQL per lot <sup>5</sup>      |

| Dimensions                                                        | MIL 2016              | 2.50%         | 2.50%        | 0.65%       | %AQL per lot <sup>5</sup>      |

| Solderability                                                     | MIL 2003              | 2.50%         | 2.50%        | 0.65%       | %AQL per lot <sup>5</sup>      |

| Lead Integrity & Lead Pull                                        | MIL 2004              | 2.50%         | 2.50%        | 0.65%       | %AQL per lot <sup>5</sup>      |

| Mark Permanency                                                   | MIL2015               | 2.50%         | 2.50%        | 0.65%       | %AQL per lot <sup>5</sup>      |

|                                                                   |                       |               |              |             |                                |

| Product Integrity                                                 |                       |               |              |             |                                |

| Design Rule and LVS Checks                                        | Crystal Spec.         | yes           | yes          | yes         |                                |

| Design for Reliability & Packaging                                | Crystal Spec.         | yes           | yes          | yes         |                                |

| Product Characterization                                          | Crystal Spec.         | limited       | full         | statistical |                                |

| Test guardbands                                                   | Crystal Spec.         | some          | 100%         | 100%        |                                |

| 5                                                                 |                       |               |              |             |                                |

| Construction Analysis                                             |                       |               |              |             |                                |

| Wafer cross section & topo                                        | Crystal Spec.         | yes           | yes          | yes         |                                |

| SEM metallization                                                 | MIL 2018              | yes           | yes          | yes         |                                |

| Package                                                           | Crystal Spec.         | yes           | ves          | yes         |                                |

| •                                                                 |                       |               |              |             | 1                              |

| Notes: 1. at High Temperatures (exc. Lev.IV)<br>2. Point Estimate |                       |               |              |             |                                |

| 3. 55°C, 0.7eV, 60%UCL                                            |                       |               |              |             |                                |

| 4. #fails/n                                                       |                       |               |              |             |                                |

| 5. LTPD and AQL criteria in table above apply                     |                       | i.            |              |             |                                |

| CUM LTPD and AQL numbers are also req                             |                       |               |              |             |                                |

| Individual Lot<br>5% LTPD                                         | Cum Lot Req<br>3% LTF |               |              |             |                                |

| 3% LTPD<br>3% LTPD                                                | 1% LTF                |               |              |             |                                |

| 2.5% AQL                                                          | 1.0% A0               | QL            |              |             |                                |

| <ol><li>Individual product performance may be obtained.</li></ol> | ained by contactin    | a a Crystal S | ales Represe | ntative     |                                |

6. Individual product performance may be obtained by contacting a Crystal Sales Representative.

1

**QUALITY AND RELIABILITY INFORMATION**

# • Notes •

|                    | GENERAL INFORMATION                                                               | 1  |

|--------------------|-----------------------------------------------------------------------------------|----|

| LAN:               | ETHERNET PRODUCTS                                                                 | 2  |

|                    | 10 Base-T ISA Controller<br>Ethernet/Cheapernet Transceiver                       |    |

| TELECOM:           | T1 / E1 PRODUCTS                                                                  | 3  |

|                    | T1 Framers<br>T1/E1 Line Interface ICs<br>Quartz Crystals                         |    |

|                    | JITTER ATTENUATORS                                                                | 4  |

|                    | DTMF RECEIVER                                                                     | 5  |

| SIGNAL PROCESSING: | VOICEBAND & BASEBAND PRODUCTS                                                     | 6  |

|                    | Echo Cancellers<br>TDMA Baseband Cellular CODEC<br>Modem / Audio Analog Front-end |    |

| DATACOM:           | INFRARED TRANSCEIVER                                                              | 7  |

| OTHER PRODUCTS:    | CONSUMER AUDIO PRODUCTS                                                           | 8  |

|                    | DATA ACQUISITION PRODUCTS                                                         | 9  |

|                    | MULTIMEDIA AUDIO PRODUCTS                                                         | 10 |

| MISCELLANEOUS:     | APPLICATION NOTES                                                                 | 11 |

|                    | APPENDICES                                                                        | 12 |

|                    | Reliability Calculation Methods<br>Package Mechanical Drawings                    |    |

|                    | SALES OFFICES                                                                     | 13 |

#### INTRODUCTION

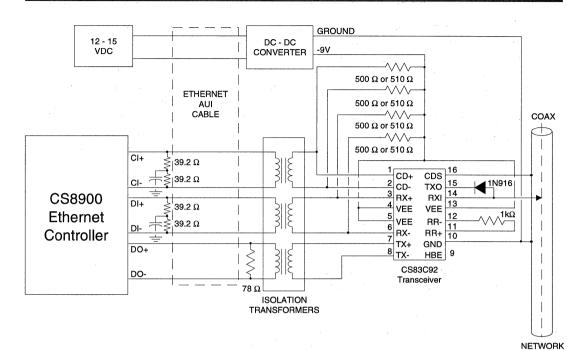

Crystal Semiconductor offers a complete Ethernet hardware solution, consisting of the CS8900 ISA-bus, 10BASE-T controller (with AUI port), and the CS83C92C coaxial-cable transceiver.

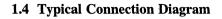

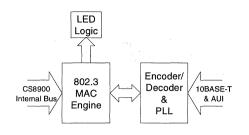

#### **CS8900 Ethernet Controller**

The CS8900 is a low-cost Ethernet LAN Controller optimized for ISA PC motherboards. Its highly-integrated design results in the industry's smallest-footprint solution. The small footprint results from the 14mm by 14mm 100-pin TQFP package, and through the elimination of external components. The CS8900 includes on-chip RAM, 10BASE-T transmit and receive filters, and a no-glue ISA-Bus interface with 24 mA drivers. In addition to saving cost and board space, the internal filters simplify the task of achieving FCC Part 15 Class B certification.

Crystal provides a complete set of certified CS8900 drivers for all major operating systems and network operating systems. Motherboard applications are further supported by the following leadership performance-oriented features: advanced power management, full-duplex operation, Stream Transfer<sup>TM</sup>, and DMA-auto-switch. The CS8900's patented PacketPage<sup>TM</sup> architecture automatically adapts to changing network traffic patterns and available system resources. The result is increased system efficiency and minimized CPU overhead.

#### **ETHERNET/CHEAPERNET IC's**

#### CS83C92 Ethernet Transceiver

Crystal is the first company to bring the benefits of low-power CMOS technology to Ethernet/Cheapernet transceivers. The CS83C92C uses up to 40 percent less power than the DP8392A and DP8392B. This translates into increased reliability and compatibility with surface-mount technology. The CS83C92C is the first Ethernet transceiver that is fully compliant with ISO/IEEE 802.3.

#### **CONTENTS**

CS83C92A/C Coaxial Transceiver Interface CS8900 Highly-Integrated ISA Ethernet Controller 2-3 2-17

# **Coaxial Transceiver Interface**

## Features

- Implemented in High Voltage, Low Power CMOS

- Compatible with National's DP8392A

- CS83C92C is Compliant With ISO/IEEE 802.3 10Base5 (Ethernet) and 10Base2 (Cheapernet)

- All Transceiver Functions Integrated Except Signal and Power Isolation

- Squelch Circuitry Rejects Noise

- CD Heartbeat Externally Selectable Allowing Operation with IEEE 802.3 Compatible Repeaters

- Receive & Transmit Mode Collision Detection

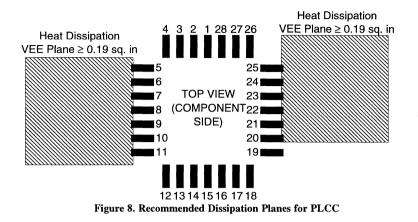

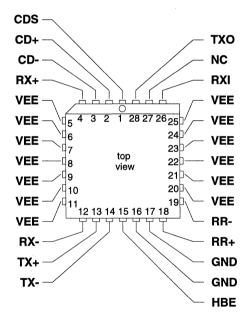

- Standard 16-pin DIP Package & 28 pin PLCC

## **General Description**

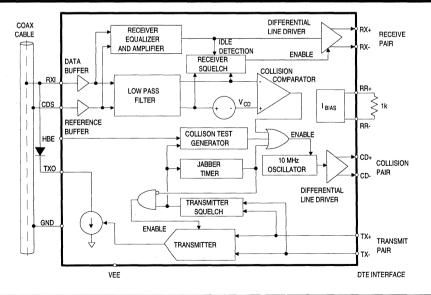

The CS83C92 Ethernet Transceiver interfaces an Ethernet or Cheapernet Local Area Network (LAN) to a LAN Adapter board, and may be located up to 50 meters from the station equipment. The Transceiver operates with the Crystal LAN components CS8005 Ethernet Data Link Controller and the CS8023A Manchester Code Converter. The CS83C92A is fully compatible with the DP8392A but the CS83C92A is built in CMOS technology (hence the 83"C"92). The CS83C92C is a higher performance grade which is compliant with IEEE 802.3 specifications.

For Ethernet applications, the CS83C92 is mounted on the COAX cable, and connects to the station equipment via an AUI cable. In a Cheapernet network, the CS83C92 is usually mounted on the LAN adapter card in the station equipment where it connects to the thin COAX through a BNC connector.

#### **ORDERING INFORMATION:**

| CS83C92A-CP | PDIP | CS83C92C- |

|-------------|------|-----------|

| CS83C92A-CL | PLCC | CS83C92C- |

CS83C92C-CP PDIP CS83C92C-CL PLCC

*Crystal Semiconductor Corporation P.O. Box 17847, Austin, TX 78760* (512) 445-7222 *Fax:* (512) 445-7581

Copyright © Crystal Semicondutor Corporation 1994 (All Rights Reserved) OCT '93 DS79F3 2-3

## **ABSOLUTE MAXIMUM RATINGS**

| Parameter                                                                 | Syı     | mbol | Min       | Max                            | Units          |

|---------------------------------------------------------------------------|---------|------|-----------|--------------------------------|----------------|

| DC Supply (referenced to ground)                                          | V       | ΈE   | -         | -12.0                          | V              |

| Package Power Rating at 25°C (No                                          | te 1) F | Pp   | -         | 3.5                            | W              |

| Input Voltage (All pins except RXI)                                       | \<br>\  | /in  | GND + 0.3 | VEE - 0.3                      | V              |

| Input Voltage on RXI                                                      | \<br>\  | /in  | GND + 0.3 | -12                            | V              |

| I/O Current (RXI, RR+, TX+, TX-, CDS, F<br>(T<br>(Note 2) (CD+, CD-, RX+, | xo)     | DUT  | -         | ±10<br>+10 / -100<br>+40 / -10 | mA<br>mA<br>mA |

| Ambient Operating Temperature                                             | -       | TA   | 0         | 70                             | ° °C           |

| Storage Temperature                                                       | Т       | stg  | -65       | 150                            | °C             |

| ESD Protection (All )                                                     | oins)   |      | 1000      | -                              | v              |

WARNING: Operation at or beyond these limits may result in permanent damage to the device. Normal operation is not guaranteed at these extremes.

Notes: 1. Plastic DIP package only, package is PC board mounted. Derate at the rate of 28.6 mW/°C.

2. Transient currents of up to 200mA will not cause SCR latch-up.

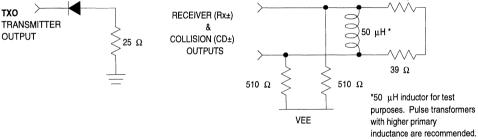

## CS83C92A ELECTRICAL CHARACTERISTICS (TA = 0° to 70°C, VEE = $-9.0V \pm 5\%$ ,

$GND = 0V, CD\pm, RX\pm pull downs = 510\Omega$ )

| Parameter                                                   | Symbol           | Min   | Тур         | Max         | Units    |

|-------------------------------------------------------------|------------------|-------|-------------|-------------|----------|

| Recommended Supply Voltage                                  | VEE              | -     | -9.0        | -           | v        |

| Supply Current (VEE to GND) Nontransmitting<br>Transmitting |                  | -     | -55<br>-100 | -70<br>-120 | mA<br>mA |

| Receiver Input Bias Current (RXI)                           | I <sub>RXI</sub> | -2    | -           | +25         | μA       |

| Transmitter Output DC Current (TXO)                         | Ітрс             | 37    | 41          | 45          | mA       |

| Transmitter Output AC Current (TXO)                         | ITAC             | ±28   | -           | ITDC        | mA       |

| Collision Threshold (Receive Mode)                          | VCD              | -1.45 | -1.53       | -1.58       | V        |

| Differential Output Voltage (RX±, CD±) (Note 3)             | Vod              | ±475  | -           | ±1200       | mV       |

| DC Common Mode Output Voltage (RX±, CD±) (Note 4)           | Voc              | -     | -2.0        | -           | V        |

| Idle State Differential Offset Voltage (RX±, CD±)           | VOB              | -     | -           | ±40         | mV       |

| Transmitter Squelch Threshold (TX±) (Note 5)                | VTS              | -175  | -225        | -300        | mV       |

| RXI Capacitance                                             | Сх               | -     | 1.2         | -           | pF       |

| Shunt Resistance - Nontransmitting (RXI)                    | R <sub>RXI</sub> | 100   | -           | -           | kΩ       |

| Shunt Resistance - Transmitting                             | Втхо             | 10    | -           | -           | kΩ       |

3. Improved Spec. as required to meet ISO/IEEE 802.3 specifications. Notes:

4. Voc has no impact on system performance since twisted pairs are transformer isolated.

5. For a minimum pulse width of  $\geq$  40 ns.

# CS83C92C ELECTRICAL CHARACTERISTICS (TA = 0° to 70°C, VEE = -9.0V ±5%,

$GND = 0V, CD\pm, RX\pm pull downs = 510\Omega$ )

| Parameter                                                                                                                    | Symbol            | Min   | Тур         | Max         | Units          |

|------------------------------------------------------------------------------------------------------------------------------|-------------------|-------|-------------|-------------|----------------|

| Recommended Supply Voltage                                                                                                   | VEE               | -     | -9.0        | -           | v              |

| Supply Current (VEE to GND) Nontransmitting<br>Transmitting                                                                  | IEE               | -     | -55<br>-100 | -65<br>-120 | mA<br>mA       |

| Receiver Input Bias Current (RXI)                                                                                            | I <sub>RXI</sub>  | -2    | -           | +25         | μΑ             |

| Transmitter Output DC Current (TXO)                                                                                          | ITDC              | 37    | 41          | 45          | mA             |

| Transmitter Output AC Current (TXO)                                                                                          | ITAC              | ±28   | -           | ITDC        | mA             |

| Collision Threshold (Receive Mode)                                                                                           | VCD               | -1.45 | -1.53       | -1.58       | v              |

| Differential Output Voltage (RX±, CD±) (Note 3)                                                                              | VOD               | ±550  | -           | ±1200       | mV             |

| DC Common Mode Output Voltage (RX±, CD±) (Note 4)                                                                            | Voc               | -     | -2.0        | -           | V              |

| Idle State Differential Offset Voltage (RX±, CD±)                                                                            | Vob               | -     | -           | ±40         | mV             |

| Transmitter Squelch Threshold (TX±) (Note 5)                                                                                 | VTS               | -175  | -225        | -300        | mV             |

| Tap Capacitance(Note 6)                                                                                                      | Сх                | -     | 1.2         | 4           | pF             |

| Shunt Resistance - Nontransmitting (RXI)                                                                                     | R <sub>RXI</sub>  | 100   | -           | -           | kΩ             |

| Shunt Resistance - Transmitting                                                                                              | Rtxo              | 10    | -           | -           | kΩ             |

| Current Sink Limit (-10 V on coax) (Notes 3, 6)                                                                              | lt <sub>10</sub>  | -     | -           | ±250        | mA             |

| Harmonic Content Relative to Fundamental (Note 7)<br>2nd and 3rd Harmonics<br>4th and 5th Harmonics<br>6th and 7th Harmonics | -20<br>-30<br>-40 |       |             | -<br>-      | dB<br>dB<br>dB |

Notes: 3. Improved Spec. as required to meet ISO/IEEE 802.3 specifications.

4. V<sub>OC</sub> has no impact on system performance since twisted pairs are transformer isolated.

5. For a minimum pulse width of  $\geq$  40 ns.

6. Measured with external diode in place (between coax center conductor and TXO pin). The maximum diode capacitance is 1pF. Tap capacitance guaranteed by characterization.

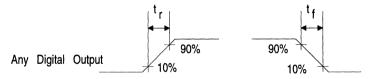

7. Guaranteed through characterization, and production measurement of rise and fall times.

## RECOMMENDED OPERATING CONDITIONS

| Parameter                         | Min  | Тур | Max  | Units<br>V |  |

|-----------------------------------|------|-----|------|------------|--|

| DC Supply Voltage, VEE (GND = 0V) | 8.55 | -   | 9.45 |            |  |

| Operating Temperature             | 0    | -   | 70   | °C         |  |

| RR± Resistor                      | 990  | -   | 1010 | Ω          |  |

# **CS83C92A SWITCHING CHARACTERISTICS** (TA = 0° to 70°C, VEE = -9.0 V $\pm$ 5%, GND = 0V, CD±, RX± pull downs = 510Ω)

| Parameter                                                      | Symbol          | Min       | Тур        | Max  | Units |

|----------------------------------------------------------------|-----------------|-----------|------------|------|-------|

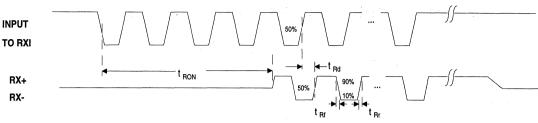

| Receiver Startup Delay (RXI to RX±)                            | tRON            | -         | 4          | 5    | bits  |

| Receiver Propagation Delay (RXI to RX±)                        | t <sub>Rd</sub> |           | 15         | 50   | ns    |

| Differential Outputs Rise Time (RX±, CD±)                      | t <sub>Rr</sub> |           | 4          | 7    | ns    |

| Differential Outputs Fall Time (RX±, CD±)                      | t <sub>Rf</sub> | ·· -      | 4          | 7    | ns    |

| Receiver and Cable Total Jitter                                | t <sub>RJ</sub> | .=        | ±2         | -    | ns    |

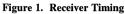

| Transmitter Start-up Delay                                     | ttst            | -         | 1          |      | bits  |

| Transmitter Propagation Delay                                  | t⊤d             | -         | 25         | 50   | ns    |

| Transmitter Rise Time - 10% to 90% (TXO)                       | t⊤r             | 20        | 25         | 30   | ns    |

| Transmitter Fall Time - 10% to 90% (TXO)                       | tTf             | 20        | 25         | 30   | ns    |

| t <sub>Tr</sub> and t <sub>Tf</sub> Mismatch                   | tтм             | -         | 0.5        | -    | ns    |

| Transmitter Skew (TXO) (Note 8)                                | t⊤s             | -         | ±0.5       | -    | ns    |

| Transmit Turn-on Pulse Width at V <sub>TS</sub> (TX±) (Note 9) | <b>t</b> TON    | · · · - · | 20         | 40   | ns    |

| Transmit Turn-off Pulse Width above $V_{TS}$ (TX±)             | <b>t</b> TOFF   |           | 250        | -    | ns    |

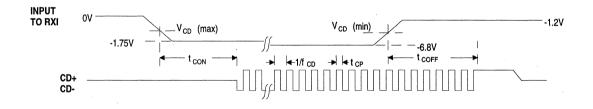

| Collision Turn-on Delay                                        | tCON            | -         | 7          | -    | bits  |

| Collision Turn-off Delay                                       | tCOFF           |           | . <b>-</b> | 20   | bits  |

| Collision Frequency (CD±)                                      | fcp             | 8.0       | -          | 12.5 | MHz   |

| Collision Pulse Width (CD±)                                    | tCP             | 35        | -          | 70   | ns    |

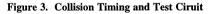

| CD Heartbeat Delay (TX± to CD±)                                | tHON            | 0.6       | -          | 1.6  | μs    |

| CD Heartbeat Duration (CD±)                                    | tHW             | 0.5       | 1.0        | 1.5  | μs    |

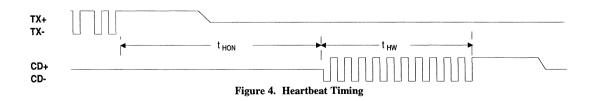

| Jabber Activation Delay (TX± to TXO and CD±)                   | tja             | 20        | 29         | 60   | ms    |

| Jabber Reset Timeout (TX± to TXO and CD±)                      | tJR             | 250       | 500        | 750  | ms    |

Notes: 8. Difference in propagation delay in outputing a positive edge as opposed to a negative edge. 9. For minimum pulse amplitude of  $\geq$  -300mV.

# CS83C92C SWITCHING CHARACTERISTICS (TA = $0^{\circ}$ to 70°C, VEE = -9.0 V ±5%,

$GND = 0V, CD\pm, RX\pm pull downs = 510\Omega$ )

| Parameter                                         | -            | Symbol           | Min | Тур  | Max  | Units |

|---------------------------------------------------|--------------|------------------|-----|------|------|-------|

| Receiver Startup Delay (RXI to RX±)               |              | t <sub>RON</sub> | -   | 4    | 5    | bits  |

| Receiver Propagation Delay (RXI to RX±)           | tRd          | -                | 15  | 50   | ns   |       |

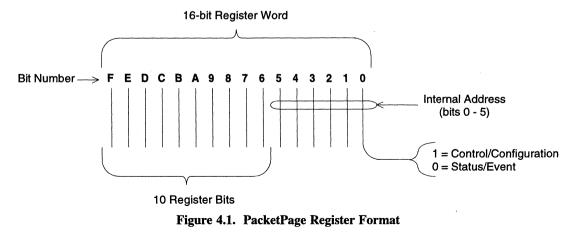

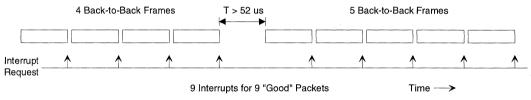

| Differential Outputs Rise Time (RX±, CD±)         | (Note 3)     | t <sub>Rr</sub>  | -   | 4    | 7    | ns    |